IDT71215S10PF Integrated Device Technology, Inc., IDT71215S10PF Datasheet

IDT71215S10PF

Specifications of IDT71215S10PF

Available stocks

Related parts for IDT71215S10PF

IDT71215S10PF Summary of contents

Page 1

... IN 2IN Write Through Bit / S IN 3IN The IDT logo is a registered trademark of Integrated Device Technology, Inc. Pentium is a trademark of Intel Corporation COMMERCIAL TEMPERATURE RANGE 1996 Integrated Device Technology, Inc. BiCMOS StaticRAM 240K (16K x 15-BIT) CACHE-TAG RAM For the Pentium Processor This high-speed MATCH signal, with t provides the fastest possible enabling of secondary cache accesses ...

Page 2

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM PIN CONFIGURATION DTY / ...

Page 3

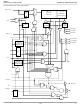

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM FUNCTIONAL BLOCK DIAGRAM ADDR (0:13) CS1 CS2 Reg TAG (0:11) OET WRITE (pos) PULSE GENERATOR WET Reg WES CLK RESET (neg) PULSE GENERATOR RESET PWRDN SFUNC W/ R BRDYH BRDYIN Reg BRDYOE 0 Reg MEMORY ...

Page 4

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TRUTH TABLES CHIP SELECT, RESET, AND POWER-DOWN FUNCTIONS CS2 CLK CS1 RESET PWRDN RESET WET WET WES CS1 PWRDN CHIP SELECT FUNCTION ...

Page 5

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TRUTH TABLES (CONT.) ( MATCH FUNCTION CS2 SFUNC CS1 OET WET WES CS1 OET WET WES ...

Page 6

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM RECOMMENDED DC OPERATING CONDITIONS Symbol Parameter Min. V Supply Voltage 4. Output Buffers 4.75 CCQ V 3.3V Output Buffers 3.0 CCQ V Supply Ground Input High Voltage 2.2 IH ...

Page 7

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM AC ELECTRICAL CHARACTERISTICS (V = 5. CCQ Symbol Parameter Read Cycle t Address Access Time Tag Bits AAT t Chip Select Access Time Tag Bits ACST (1) t Chip ...

Page 8

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM AC ELECTRICAL CHARACTERISTICS (V = 5. CCQ Symbol Parameter Write Cycle and Clock Parameters t Clock Cycle Time CYC ( Clock Pulse HIGH CH ( ...

Page 9

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM AC ELECTRICAL CHARACTERISTICS (V = 5. CCQ Symbol Parameter MATCH and Cycles BRDY BRDY t Address to MATCH Valid ADM t Data Input to MATCH Valid DAM t Chip ...

Page 10

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM AC TEST CONDITIONS Input Pulse Levels Input Rise/Fall Times Input Timing Reference Levels Output Timing Reference Levels AC Test Load AC TEST LOADS V CCQ Outputs 347 Figure 1. AC Test Load Tag I/O and ...

Page 11

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF WRITE AND READ CYCLES COMMERCIAL TEMPERATURE RANGE 14.3 11 ...

Page 12

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF MATCH AND FUNCTIONS BRDY BRDY 14.3 COMMERCIAL TEMPERATURE RANGE 12 ...

Page 13

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF RESET RESET CLK t SR RESET t PDSR PWRDN VLD OUT DTY OUT WT OUT t S WES WET BRDY MATCH TAG (0:11) NOTE: 1. Transition is measured 200mV from steady state. ...

Page 14

IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF OES OES OES VLD OUT DTY OUT Valid Output WT OUT NOTE: 1. Transition is measured 200mV from steady state. TIMING WAVEFORMS OF POWER DOWN FUNCTION PWRDN t WHPL CLK t RHPL ...