mpc92439 Integrated Device Technology, mpc92439 Datasheet

mpc92439

Available stocks

Related parts for mpc92439

mpc92439 Summary of contents

Page 1

... Low Voltage, LVPECL Clock Syntheesizer The MPC92439 is a 3.3 V compatible, PLL based clock synthesizer targeted for high performance clock generation in mid-range to high-performance telecom, networking and computing applications. With output frequencies from 3.125 MHz to 900 MHz and the support of differential LVPECL output signals the device meets the needs of the most demanding clock applications ...

Page 2

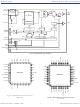

... T-LATCH 1 BITS 0 GND 26 TEST MPC92439 29 GND FOUT 30 31 FOUT Figure 3. MPC92439 32-Lead Package Pinout (Top View) ©2009 Integrated Device Technology, Inc. FOUT FOUT TEST M[3] 14 M[2] 13 M[1] 12 M[0] 11 P_LOAD XTAL_OUT 7 8 ...

Page 3

... MPC92439 GND 29 30 FOUT 31 FOUT Figure 4. 32-Lead VFQFN Package Pinout (Top View) MPC92439 REVISION 4 OCTOBER 27, 2009 M[3] M[ M[0] 11 P_LOAD XTAL_OUT 900MHZ, LOW VOLTAGE, LVPECL CLOCK SYNTHESIZER ©2009 Integrated Device Technology, Inc. ...

Page 4

... MPC92439 REVISION 4 OCTOBER 27, 2009 Default Type 6 Analog Crystal oscillator interface 0 LVCMOS Alternative PLL reference input LVPECL Differential clock output LVCMOS Test and device diagnosis output 1 LVCMOS PLL reference select input 0 LVCMOS Configuration input for power down mode. Assertion (deassertion) of power down will decrease (increase) the output frequency by a ratio discrete steps ...

Page 5

... S 1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied. MPC92439 REVISION 4 OCTOBER 27, 2009 0 FREF_EXT (FOUT = L, FOUT = H) Output divider ÷ ...

Page 6

... The frequency of S_CLOCK is limited to 10 MHz in serial programming mode. S_CLOCK can be switched at higher frequencies when used as test clock in test mode 6. See 4. Maximum cycle jitter measured at the lowest VCO frequency. 5. Maximum period jitter measured at the lowest VCO frequency. MPC92439 REVISION 4 OCTOBER 27, 2009 = 3.3V ± 5 0°C to +70°C) CC ...

Page 7

... MPC92439 Data Sheet Table 8. MPC92439 Frequency Operating Range (in MHz) VCO frequency for an crystal interface frequency of M M[6: 0010100 21 0010101 22 0010110 23 0010111 24 0011000 25 0011001 26 0011010 27 0011011 28 0011100 29 0011101 30 0011110 31 0011111 32 0100000 33 0100001 34 0100010 35 0100011 36 0100100 37 0100101 38 0100110 39 0100111 40 0101000 400 41 0101001 410 ...

Page 8

... Figure 6 illustrate the RMS jitter performance of the MPC92439 across its specified VCO frequency range. The cycle-to- cycle and period jitter is a function of the VCO frequency and the output divider N. The general trend is that as the output frequency increases (higher VCO frequency and lower N-divider) the MPC92439 output jitter decreases ...

Page 9

... MPC92439 itself. However, the PLL bypass mode may be of interest at the board level for functional debug. When T[2:0] is set to 110 the MPC92439 is placed in PLL bypass mode. In this mode the S_CLOCK input is fed directly into the M and N dividers. The N divider drives the FOUT differential pair and the M counter drives the TEST output pin ...

Page 10

... The crystal, the trace and optional capacitors should be placed on the board as close as possible to the MPC92439 XTAL_IN and XTAL_OUT pins to reduce crosstalk of active signals into the oscillator. Short and wide traces further reduce parasitic inductance and resistance further recommended to guard the crystal circuit by placing a ground ring around the traces and oscillator components ...

Page 11

... MPC92439 will be a approximately 350-400 ppm higher than using crystals specified for parallel frequency mode. This is applicable to applications using the MPC92439 in sockets designed for the pin and function compatible MC12439 synthesizer, which has an oscillator using the crystal in its series resonance mode ...

Page 12

... MPC92439 Data Sheet Package Outline and Package Dimensions MPC92439 REVISION 4 OCTOBER 27, 2009 900MHZ, LOW VOLTAGE, LVPECL CLOCK SYNTHESIZER PACKAGE DIMENSIONS CASE 776-02 ISSUE D PLCC PLASTIC PACKAGE 12 ©2009 Integrated Device Technology, Inc. ...

Page 13

... MPC92439 Data Sheet D1/2 PIN 1 INDEX E1 D/2 4X 0. 28X SEATING PLANE (S) A1 DETAIL AD MPC92439 REVISION 4 OCTOBER 27, 2009 PACKAGE DIMENSIONS 4X 0. DETAIL G E 32X 0.1 C DETAIL AD PLATING METAL (θ1˚) 0. SECTION F ...

Page 14

... 0. 0.25 Ref. b 0.18 0.25 N & & E 5.00 Basic D2 & E2 3.0 e 0.50 Basic L 0.30 0.40 Reference Document: JEDEC Publication 95, MO-220 MPC92439 REVISION 4 OCTOBER 27, 2009 -1 ef Anvil Anvil Singula tion Sawn (Ref.) N & N Odd Bottom View w/Type B ID ...

Page 15

... MPC92439 Data Sheet 6024 Silver Creek Valley Road Sales 800-345-7015 (inside USA) San Jose, California 95138 +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT’s sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice ...