mpc92469 Integrated Device Technology, mpc92469 Datasheet

mpc92469

Available stocks

Related parts for mpc92469

mpc92469 Summary of contents

Page 1

... MHz Low Voltage PECL Clock Synthesizer w/Spread Spectrum The MPC92469 is a 3.3 V compatible, PLL based clock synthesizer targeted for high performance clock generation in mid-range to high-performance tele- com, networking and computing applications. With output frequencies from 25 MHz to 400 MHz and the support of differential PECL output signals the device meets the needs of the most demanding clock applications ...

Page 2

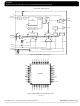

... SHIFT REGISTER Figure 1. MPC92469 Logic Diagram MPC92469 Figure 2. MPC92469 32-Lead Package Pinout (Top View FOUT OE 10 FOUT 11 SYNC TEST TEST 3 2 T-LATCH SSM-LATCH 0 BITS 4-6 BITS 0 M[3] 14 M[2] 13 ...

Page 3

... PLL positive power supply (analog power supply). CC Output Division Function output low stops F in the logic low state OUT pins must be connected to the CC Output Frequency Range 200 – 400 MHz 100 – 200 MHz 50 – 100 MHz 25 – 50 MHz MPC92469REV 4 JANUARY 23, 2007 ...

Page 4

... Maximum Supply Current CC 1. Inputs have pull-down resistors affecting the input current. 2. Outputs terminated 50 Ω The MPC92469 TEST output levels are compatible to the MC12429 output levels. IDT™ / ICS™ PECL CLOCK SYNTHESIZER W/SPREAD SPECTRUM Min 200 2000 200 ...

Page 5

... MHz 200 MHz 100 MHz 50 MHz 0.3 ns 20% to 80% 10 MHz ≠ ≠ kHz MHz XTAL ±0.30 ±0 300 MHz out -0.3 -0 MHz XTAL x M ÷ VCO XTAL MPC92469REV 4 JANUARY 23, 2007 ...

Page 6

... M is the PLL feedback- XTAL divider and N is the PLL post-divider. The input frequency and the selection of the feedback divider M is limited by the VCO-frequency range. f and M must be configured to XTAL Table 7. MPC92469 Frequency Operating Range VCO frequency for a crystal interface frequency of M M[8: 160 ...

Page 7

... MPC92469 itself. However the PLL bypass mode may be of interest at the board level for functional debug. When T[2:0] is set to 110 the MPC92469 is placed in PLL bypass mode. In this mode the S_CLOCK input is fed directly into the M and N dividers. The N divider drives ...

Page 8

... Figure 4. Down Spread % across VCO Range with 16 MHz Reference Figure 5. Center Spread % across VCO Range with 16 MHz Reference IDT™ / ICS™ PECL CLOCK SYNTHESIZER W/SPREAD SPECTRUM SS2 SS1 SS0 Figure 3. Serial Interface Timing Diagram Last Bit MPC92469REV 4 JANUARY 23, 2007 ...

Page 9

... IDT™ / ICS™ PECL CLOCK SYNTHESIZER W/SPREAD SPECTRUM filter on the V illustrates a typical power supply filter scheme. The MPC92469 is most susceptible to noise with spectral content in the 1 kHz to 1 MHz range. Therefore, the filter should be designed to target this range. The key parameter that needs ...

Page 10

... XTAL_IN and XTAL_OUT pins to ground may be used to trim the frequency as shown in Figure 8. The crystal and optional trim capacitors should be located as close to the MPC92469 XTAL_IN and XTAL_OUT pins as possible to avoid any board level parasitic. Table 12. Recommended Crystal Specifications Parameter ...

Page 11

... ˚ MPC92469REV 4 JANUARY 23, 2007 ...

Page 12

... MPC92469 400MHZ, LOW VOLTAGE, PECL CLOCK SYNTHESIZER W/SPREAD SPECTRUM Innovate with IDT and accelerate your future networks. Contact: www.IDT.com For Sales For Tech Support 800-345-7015 netcom@idt.com 408-284-8200 480-763-2056 Fax: 408-284-2775 Corporate Headquarters Asia Pacific and Japan Integrated Device Technology, Inc. Integrated Device Technology 6024 Silver Creek Valley Road Singapore (1997) Pte ...