74ac651 IK Semicon Co., Ltd, 74ac651 Datasheet

74ac651

Related parts for 74ac651

74ac651 Summary of contents

Page 1

... Octal 3-State Bus Transceivers and D Flip-Flops High-Speed Silicon-Gate CMOS The IN74AC651 is identical in pinout to the LS/ALS651, HC/HCT651. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LS/ALS outputs. These devices consists of bus transceiver circuits, D-type flip-flop, and control circuitry arranged for multiplex transmission of data directly from the data bus or from the internal storage registers ...

Page 2

... Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V outputs must be left open. Parameter and GND Pins CC SOIC Package+ Parameter * and V should be constrained to the range GND≤(V IN OUT IN74AC651 Value Unit -0.5 to +7 ±20 mA ±50 mA ±50 mA 750 mW 500 ° ...

Page 3

... I = = = GND 5 (OE)= 5 GND GND OUT CC V =1.65 V Max 5.5 OLD V =3.85 V Min 5.5 OHD GND 5 IN74AC651 Guaranteed Limits 25 °C Unit -40°C to 85°C 2.1 2.1 V 3.15 3.15 3.85 3.85 0.9 0.9 V 1.35 1.35 1.65 1.65 2.9 2.9 V 4.4 4.4 5.4 5.4 2.56 2.46 3.86 3.76 4.86 4.76 0.1 0.1 V 0.1 0.1 0.1 0.1 0.36 0.44 0.36 0.44 0.36 0.44 ±0.1 ±1.0 μA ±0.6 ± ...

Page 4

... Power Dissipation Capacitance PD Voltage Range 3 3.3 V ±0 Voltage Range 5 5.0 V ±0 =50pF,Input t =t =3.0 ns Guaranteed Limits CC 25 °C V Min Max Min 3.3 4.0 17.0 3.0 5.0 2.5 12.0 2.0 3.3 3.0 14.5 2.5 5.0 2.0 10.5 1.5 3.3 3.0 14.0 2.5 5.0 2.0 9.5 1.5 3.3 2.5 13.0 2.0 5.0 1.5 9.0 1.0 3.3 3.0 14.0 2.5 5.0 2.5 10.0 2.0 3.3 2.5 13.5 2.0 5.0 2.0 10.0 1.5 3.3 2.5 12.0 2.0 5.0 1.5 9.0 1.0 3.3 2.5 12.0 2.0 5.0 1.5 9.0 1.0 3.3 3.0 13.0 2.5 5.0 2.0 11.0 1.5 3.3 2.5 12.5 2.0 5.0 2.0 10.5 1.5 3.3 3.0 12.5 2.5 5.0 2.0 9.5 1.5 3.3 2.5 12.5 2.0 5.0 1.5 9.5 1.0 3.3 3.5 13.5 3.0 5.0 2.5 11.5 2.0 3.3 3.0 13.5 2.5 5.0 2.5 11.5 2.0 5.0 4.5 5.0 15 Typical @25°C,V =5 IN74AC651 Unit -40°C to 85°C Max 19.0 ns 14.0 16.5 ns 12.0 16.0 ns 11.0 15.0 ns 10.5 16.0 ns 11.5 15.5 ns 11.5 13.5 ns 10.0 14.0 ns 10.5 14.0 ns 12.0 14.0 ns 12.0 14.0 ns 10.5 14.5 ns 11.0 14.5 ns 12.5 15.0 ns 13.0 4 Rev. 00 ...

Page 5

... Minimum Setup Time Data Port to-B Clock or B-to-A Clock (Figure 7) t Minimum Hold Time, A-to-B Clock or h B-to-A Clock Data Port (Figure 7) t Minimum Pulse Width, A-to-B Clock or w B-to-A Clock (Figure 7) =50pF,Input t =t =3.0 ns °C V 5.0 5.0 5.0 TIMING DIAGRAM IN74AC651 Guaranteed Limits Unit -40°C to 85°C 7.0 8.0 ns 2.5 2.5 ns 6.0 7.0 ns Rev. 00 ...

Page 6

... OUTPUTS Both the A bus and the B bus are outputs The data stored to the internal flip-flops are displayed at the A and B bus respectively The output at the A bus are displayed at the B bus, the output at the B bus are displayed at the A bus respec. IN74AC651 FUNCTION Rev. 00 ...

Page 7

... SWITCHING DIAGRAMS Figure 1. Switching Waveforms Figure 2. A Data Port = Input, B Data Port = Output Figure 4. Switching Waveforms Figure 6. Switching Waveforms IN74AC651 Figure 3. A Data Port = Output, B Data Port = Input Figure 5. Switching Waveforms Figure 7. Switching Waveforms Rev. 00 ...

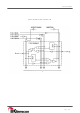

Page 8

... EXPANDED LOGIC DIAGRAM IN74AC651 Rev. 00 ...

Page 9

... A; for B ‑ 0.25 mm (0.010) per side. N SUFFIX PLASTIC DIP (MS - 001AF -T- SEATING PLANE SUFFIX SOIC (MS - 013AD SEATING PLANE IN74AC651 Dimension, mm Symbol MIN MAX A 31.24 32.51 B 6.1 7. .33 D 0.36 0.56 F 1.14 1.78 G 2. 0° 10° K 2.92 3 ...