SAA7183A Philips Semiconductors, SAA7183A Datasheet

SAA7183A

Related parts for SAA7183A

SAA7183A Summary of contents

Page 1

... DATA SHEET SAA7182A; SAA7183A Digital Video Encoder (EURO-DENC2) Preliminary specification Supersedes data of 1996 Sep 11 File under Integrated Circuits, IC22 INTEGRATED CIRCUITS 1996 Oct 02 ...

Page 2

... SAA7182AWP; PLCC84 SAA7183AWP QFP80 1996 Oct 02 This applies to SAA7183A only. The device is protected by USA patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. Use of the Macrovision anti-copy process in the device is licensed for non-commercial home use only. Reverse engineering or disassembly is prohibited. ...

Page 3

... Y, C, CVBS and RGB without load o(p-p) (peak-to-peak value) R load resistance L ILE LF integral linearity error DLE LF differential linearity error T operating ambient temperature amb 1996 Oct 02 PARAMETER 3 Preliminary specification SAA7182A; SAA7183A MIN. TYP. MAX. UNIT 3.1 3.3 3.5 V 3.0 3.3 3.6 V 4.75 5.0 5.25 V 110 ...

Page 4

... SAA7182A SAA7183A Y CbCr 5, 14, 22, 29, 38, 46, 2, 23, 40, 41 49, 80, 82 43 Fig.1 Block diagram; PLCC84. 4 Preliminary specification SAA7182A; SAA7183A TTXRQ XTALO LLC V DDA4 to V DDA9 RCV2 CREF XTALI TESTB 75 63, 64, 68, 70, 72, 74 SYNC CLOCK 2 I C-bus 8 ...

Page 5

... Y ENCODER CbCr C-bus 8 internal control control bus SAA7182A SAA7183A Y CbCr 66 65 30 Fig.2 Block diagram; QFP80. 5 SAA7182A; SAA7183A TTXRQ XTALO LLC V DDA4 to V DDA9 RCV2 CREF XTALI TESTB 63 52, 53, 56, 58, 60, 62 SYNC CLOCK 2 I C-bus 8 clock control D OUTPUT INTERFACE ...

Page 6

... Lower 4 bits of MPEG port input for “ CCIR 656 ” style multiplexed Cb data, or for Y data only line input mode is used. Raster Control 1 for video port. This pin receives/provides a VS/FS/FSEQ signal. Raster Control 2 for video port. This pin provides an HS pulse of programmable length or receives an HS pulse. 6 Preliminary specification SAA7182A; SAA7183A DESCRIPTION ...

Page 7

... Select analog input. Digital-to-analog converted RGB output when SELI = LOW; RI, GI and BI output when SELI = HIGH. not connected Analog ground 2 for the DACs. Analog supply voltage 6 for DACs (3.3 V). Analog output of the chrominance signal. Analog supply voltage 7 for the Y/C/CVBS DACs (3.3 V). 7 Preliminary specification SAA7182A; SAA7183A DESCRIPTION ...

Page 8

... Test pin. Connected to digital ground for normal operation. Test pin. Connected to digital ground for normal operation. digital ground 8 digital supply voltage 8 (3.3 V) digital ground 9 digital supply voltage C-bus serial clock input C-bus serial data input/output. 8 Preliminary specification SAA7182A; SAA7183A DESCRIPTION ...

Page 9

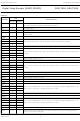

... V SSD3 24 MP7 25 MP6 26 MP5 27 MP4 28 V DDD4 29 V SSD4 30 MP3 31 MP2 32 1996 Oct 02 SAA7182A SAA7183A Fig.3 Pin configuration; PLCC84. 9 Preliminary specification SAA7182A; SAA7183A 74 V DDA9 73 CVBS 72 V DDA8 DDA7 69 CHROMA 68 V DDA6 67 V SSA2 66 n.c. 65 SELI 64 V DDA5 63 ...

Page 10

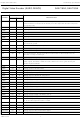

... MP6 16 MP5 17 MP4 18 V DDD4 19 V SSD3 20 MP3 21 MP2 22 MP1 23 MP0 24 1996 Oct 02 SAA7182A SAA7183A Fig.4 Pin configuration; QFP80. 10 Preliminary specification SAA7182A; SAA7183A 64 V SSA3 63 TESTB 62 V DDA9 61 CVBS 60 V DDA8 DDA7 57 CHROMA 56 V DDA6 55 V SSA2 54 SELI 53 ...

Page 11

... Decoder (SAA7111 or SAA7151B) in conjunction with a CREF clock qualifier to EURO-DENC2. Via the RTCI pin, connected to RTCO of a decoder, information concerning 1996 Oct 02 SAA7182A; SAA7183A actual subcarrier, PAL-ID, and if connected to SAA7111, definite subcarrier phase can be inserted. The EURO-DENC2 synthesizes all necessary internal signals, colour subcarrier frequency, and synchronization signals, from that clock ...

Page 12

... The internal insertion window for text is set to 360 teletext bits including clock run-in bits. For protocol and timing see Fig.19. 1996 Oct 02 SAA7182A; SAA7183A C LOSED CAPTION ENCODER Using this circuit, data in accordance with the specification of Closed Caption or Extended Data Service, delivered by the control interface, can be encoded (Line 21) ...

Page 13

... For RGB outputs variable amplification of the Y, Cb and Cr components is provided, enabling adjustment of contrast and colour saturation in certain range. Reference levels are measured with a colour bar, 100% white, 100% amplitude and 100% saturation. 13 Preliminary specification SAA7182A; SAA7183A C-bus slave addresses are selected: ...

Page 14

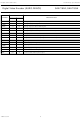

... Preliminary specification SAA7182A; SAA7183A (1) (2) ( 235 235 235 235 16 235 16 235 235 16 235 BITS ...

Page 15

... Philips Semiconductors Digital Video Encoder (EURO-DENC2) 1996 Oct 02 SAA7182A; SAA7183A 15 Preliminary specification ...

Page 16

... Philips Semiconductors Digital Video Encoder (EURO-DENC2) 1996 Oct 02 SAA7182A; SAA7183A 16 Preliminary specification ...

Page 17

... ACKs STOP condition Wide Screen Signalling bits aspect ratio enhanced services subtitles reserved wide screen signalling output is disabled wide screen signalling output is enabled DESCRIPTION 17 Preliminary specification SAA7182A; SAA7183A ACK -------- DATA n DESCRIPTION DESCRIPTION Suggested 32 32 ...

Page 18

... OVL keying disabled for Y, C and CVBS outputs. CBENB 0 Data from input ports is encoded. Default after reset. 1 Colour bar with programmable colours (entries of OVL_LUTs) is encoded. The LUTs are read in upward order from index 0 to index 7. 1996 Oct 02 SAA7182A; SAA7183A DESCRIPTION 18 Preliminary specification ...

Page 19

... VALUE tbf tbf tbf tbf 19 Preliminary specification SAA7182A; SAA7183A INDEX OVLV 0 (00H) 0 (00H) 18 (12H) 14 (0EH) 144 (90H) 172 (ACH) 162 (A2H) 185 (B9H) 94 (5EH) 71 (47H) 112 (70H) 84 (54H) 238 (EEH) ...

Page 20

... IRE BLCKL = 0 BLCKL = 63 (3FH) 25/63 + 24; recommended value: BLCKL = 60 (3CH) normal. 26/63 + 24; recommended value: BLCKL = 45 (2DH) normal. 20 Preliminary specification SAA7182A; SAA7183A REMARKS output subcarrier of U contribution = 0 output subcarrier of U contribution = nominal output subcarrier of U contribution = 0 output subcarrier of U contribution = nominal REMARKS ...

Page 21

... BLNNL = 58 (3AH) normal. 26/63 + 17; recommended value: BLNNL = 63 (3FH) normal. DESCRIPTION FUNCTION 21 Preliminary specification SAA7182A; SAA7183A REMARKS output blanking level = 17 IRE output blanking level = 42 IRE output blanking level = 17 IRE output blanking level = 43 IRE real time control input from SAA7151B ...

Page 22

... DACs for CVBS, Y and C in normal operational mode; default after reset DACs for CVBS, Y and C forced to lowest output voltage DACs for R, G and B in normal operational mode; default after reset DACs for R, G and B forced to lowest output voltage 22 Preliminary specification SAA7182A; SAA7183A DESCRIPTION ...

Page 23

... FSC round = ------- - f see note 1 = 1716 FSC = 569408543 (21F07C1FH). = 1728 FSC = 705268427 (2A098ACBH). llc = 1728 FSC = 681786290 (28A33BB2H). llc 23 Preliminary specification SAA7182A; SAA7183A DESCRIPTION REMARKS (1) nominal (2) nominal (3) nominal (4) nominal REMARKS FSC3 = most significant byte 32 2 FSC0 = least significant byte ...

Page 24

... RCV1 port (at bit SYMP = LOW) or from decoded frame sync of CCIR 656 input (at bit SYMP = HIGH); default after reset horizontal synchronization is taken from RCV2 port (at bit SYMP = LOW) defines signal type on pin RCV1; see Table 24 24 Preliminary specification SAA7182A; SAA7183A DESCRIPTION ...

Page 25

... SECAM-specific if bit SECAM = 1 reset every eight fields reset every four fields 25 Preliminary specification SAA7182A; SAA7183A FUNCTION vertical sync each field; default after reset frame sync (odd/even) field sequence, vertical sync every fourth field (PAL = 0), eighth field (PAL = 1) or twelfth field ...

Page 26

... M-systems line = (SCCLN + 1) for other systems Line 21 encoding off enables encoding in field 1 (odd) enables encoding in field 2 (even) enables encoding in both fields DESCRIPTION 26 Preliminary specification SAA7182A; SAA7183A FUNCTION DESCRIPTION FUNCTION ...

Page 27

... LINExx (50 Hz field rate) this bit mask is effective only, if the lines are enabled by TTXOVS/TTXOVE and TTXEVS/TTXEVE S UBADDRESSES In subaddresses 5B, 5C, 5D, 5E and 62 all IRE values are rounded up. 1996 Oct 02 SAA7182A; SAA7183A DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION 27 ...

Page 28

... It is set immediately after the data has been encoded. During first field of a sequence (repetition rate: NTSC = 4 fields, PAL = 8 fields, SECAM = 12 fields. Not first field of a sequence. During even field. During odd field. 28 Preliminary specification SAA7182A; SAA7183A DATA BYTE CCRDO CCRDE 0 DESCRIPTION ...

Page 29

... SCBW = 1. (2) SCBW = 0. handbook, halfpage (1) SCBW = 1. (2) SCBW = 0. 1996 Oct 02 ( Fig.5 Chrominance transfer characteristic (dB) 0 (1) ( 0.4 0.8 Fig.6 Chrominance transfer characteristic 2. 29 Preliminary specification SAA7182A; SAA7183A 10 12 MBE735 1.2 f (MHz) 1.6 MBE737 14 f (MHz) ...

Page 30

... CCRS1 = 1; CCRS0 = 1. (4) CCRS1 = 0; CCRS0 = 0. handbook, halfpage (1) CCRS1 = 0; CCRS0 = 0. 1996 Oct 02 (4) (2) (3) ( Fig.7 Luminance transfer characteristic (dB) ( Fig.8 Luminance transfer characteristic 2. 30 Preliminary specification SAA7182A; SAA7183A MBE736 6 f (MHz) MGD672 14 f (MHz) ...

Page 31

... G v (dB 1996 Oct Fig.9 Luminance transfer characteristic in RGB Fig.10 Colour difference transfer characteristic in RGB. 31 Preliminary specification SAA7182A; SAA7183A MGB708 14 f (MHz) MGB706 14 f (MHz) ...

Page 32

... Philips Semiconductors Digital Video Encoder (EURO-DENC2) handbook, full pagewidth (dB 0.2 handbook, full pagewidth 30 (deg 0.2 1996 Oct 02 0.4 0.6 0.8 Fig.11 Gain of SECAM pre-emphasis. 0.4 0.6 0.8 Fig.12 Phase of SECAM pre-emphasis. 32 Preliminary specification SAA7182A; SAA7183A 1 1.2 1.4 f (MHz) 1 1.2 1.4 f (MHz) MGB705 1.6 MGB704 1.6 ...

Page 33

... Philips Semiconductors Digital Video Encoder (EURO-DENC2) handbook, full pagewidth (dB 0.2 handbook, full pagewidth 80 (deg 0.2 1996 Oct 02 0.4 0.6 0.8 Fig.13 Gain of SECAM anti-Cloche. 0.4 0.6 0.8 Fig.14 Phase of SECAM anti-Cloche. 33 Preliminary specification SAA7182A; SAA7183A 1 1.2 1.4 f (MHz) 1 1.2 1.4 f (MHz) MGB703 1.6 MGB702 1.6 ...

Page 34

... C; unless otherwise specified. amb note 1 note 1 note 1 clocks data I/Os at high impedance note 2 note 2 note LOW or HIGH during acknowledge note 3 note 4 LLC note 3 note 3 34 Preliminary specification SAA7182A; SAA7183A CONDITIONS MIN. 3.1 3.0 4.75 0.5 2.0 2.4 0 2.4 2.6 0.5 3 MAX. UNIT 3 ...

Page 35

... For full digital range, without load, V voltage (digital zero at DAC) is 0.2 V. 1996 Oct 02 CONDITIONS 3rd harmonic note 5 note 3.3 V. The typical voltage swing is 1.4 V, the typical minimum output DDA 35 Preliminary specification SAA7182A; SAA7183A MIN. MAX. UNIT 30 MHz 50 + ...

Page 36

... HIGH t HD; DAT LLC t HIGH t HD; DAT t f valid not valid HD; DAT valid not valid Fig.15 Clock data timing. Cb(0) Y(0) Fig.16 Functional timing. 36 Preliminary specification SAA7182A; SAA7183A valid valid MBE742 Cr(0) Y(1) 2.6 V 1.5 V 0.6 V 2.4 V 1.5 V 0.8 V 2.0 V 0.8 V 2.4 V 0.6 V Cb(2) MGB699 ...

Page 37

... SAAA7111 provides ( bits, resulting in 3 reserved bits before sequence bit. 1996 Oct 02 Y(0) Y(1) Cb(0) Cr(0) Fig.17 Digital TV timing. 4 bits reserved HPLL increment not used in SAA7182A/83A Y) line inverted. Fig.18 RTCI timing. 37 Preliminary specification SAA7182A; SAA7183A Y(2) Y(3) Cb(2) Cr(2) sequence 5 bits reserved FSCPLL increment (4) valid invalid 8/LLC sample sample Y(4) Cb(4) MBE739 reserved (2) bit (1) reset bit (3) 0 ...

Page 38

... TTXOVE) plus all suitable lines of the even field (TTXEVS and TTXEVE) can be used for teletext insertion Fig.19 Teletext timing diagram. 38 Preliminary specification SAA7182A; SAA7183A t TTXWin 1/LLC 1/LLC 24 MGB701 ...

Page 39

... Philips Semiconductors Digital Video Encoder (EURO-DENC2) APPLICATION INFORMATION 1996 Oct 02 SAA7182A; SAA7183A 39 Preliminary specification pagewidth full handbook, ...

Page 40

... Philips Semiconductors Digital Video Encoder (EURO-DENC2) 1996 Oct 02 SAA7182A; SAA7183A 40 Preliminary specification pagewidth full handbook, ...

Page 41

... V is achieved, resulting in V resistor external series resistor of 27 load impedance. colour bar signal. CONVERSION RANGE (peak-to-peak Y (VBS) SYNC TIP-TO-WHITE (digits) 888 41 Preliminary specification SAA7182A; SAA7183A = 0.86 V (p-p) with an internal series o RGB (Y) BLACK-TO-WHITE AT GDY = GDC = 6 (digits) 712 ...

Page 42

... 0.81 29.41 29.41 28.70 28.70 30.35 1.27 0.66 29.21 29.21 27.69 27.69 30.10 0.032 1.158 1.158 1.130 1.130 1.195 0.05 0.026 1.150 1.150 1.090 1.090 1.185 REFERENCES JEDEC EIAJ 42 Preliminary specification SAA7182A; SAA7183A detail max. 30.35 1.22 1.44 0.51 0.18 0.18 30.10 1.07 1.02 1.195 ...

Page 43

... Oct scale (1) ( 0.45 0.25 20.1 14.1 24.2 0.8 0.30 0.14 19.9 13.9 23.6 REFERENCES JEDEC EIAJ 43 Preliminary specification SAA7182A; SAA7183A 18.2 1.0 1.4 1.95 0.2 0.2 17.6 0.6 1.2 EUROPEAN PROJECTION ...

Page 44

... The longitudinal axis of the package footprint must be parallel to the solder flow. 1996 Oct 02 SAA7182A; SAA7183A The package footprint must incorporate solder thieves at the downstream corners. QFP Wave soldering is not recommended for QFP packages. ...

Page 45

... Philips. This specification can be ordered using the code 9398 393 40011. 1996 Oct components conveys a license under the Philips’ system provided the system conforms to the I 45 Preliminary specification SAA7182A; SAA7183A 2 C patent to use the 2 C specification defined by ...