MC14559BCP ON Semiconductor, MC14559BCP Datasheet - Page 6

MC14559BCP

Manufacturer Part Number

MC14559BCP

Description

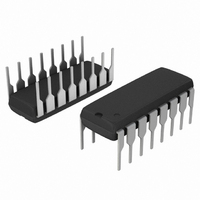

IC REGISTER 8BIT APPROX 16-DIP

Manufacturer

ON Semiconductor

Series

4000Br

Datasheet

1.MC14559BDWR2G.pdf

(9 pages)

Specifications of MC14559BCP

Logic Type

Register, Successive Approximation

Output Type

Standard

Number Of Elements

1

Number Of Bits Per Element

8

Function

Universal

Voltage - Supply

3 V ~ 18 V

Operating Temperature

-55°C ~ 125°C

Mounting Type

Through Hole

Package / Case

16-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC14559BCP

Manufacturer:

RCA

Quantity:

6 236

Externally Controlled 6−Bit ADC (Figure 2)

•

•

•

•

Continuously Cycling 8−Bit ADC (Figure 3)

signal is fed back to the SC input, immediately initiating a

new cycle on the next clock pulse.

Several features are shown in this application:

This ADC is running continuously because the EOC

Shortening of the register to six bits by feeding the

seventh output bit into the FF input.

Continuous conversion, if a continuous signal is applied

to SC.

Externally controlled updating (the start pulse must be

shorter than the conversion cycle).

The EOC output indicating that the parallel data are

valid and that the serial output is complete.

SC

SC

Figure 3. Continuously Cycling 8−Bit ADC

Figure 2. Externally Controlled 6−Bit ADC

Q7 Q6

Q7 Q6

C

C

MC14549B, MC14559B

TYPICAL APPLICATIONS

Q5

Q5

TO DAC

http://onsemi.com

Q4

Q4

TO DAC

MC14559B

Q3

MC14559B

Q3

6

Q2

Q2

Continuously Cycling 12−Bit ADC (Figure 4)

has a capability of handling only an eight−bit word, two

must be cascaded to make an ADC with more than eight bits.

SAR must have a stable resettable state to remain in while

awaiting a subsequent start signal. However, the first stage

must not have a stable resettable state while recycling,

because during switch−on or due to outside influences, the

first stage has entered a reset state, the entire ADC will

remain in a stable non−functional condition.

well as the parallel outputs are updated every thirteenth

clock pulse. The EOC pulse indicates the completion of the

12−bit conversion cycle, the end of the serial output word,

and the validity of the parallel data output.

Q1

Q1

Because each successive approximation register (SAR)

When it is necessary to cascade two SAR’s, the second

This 12−bit ADC is continuously recycling. The serial as

Q0

Q0

FF

FF

EOC

EOC

S

S

out

out