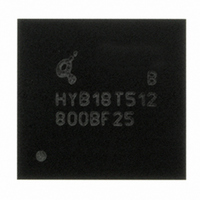

HYB18T512800BF-2.5 Qimonda, HYB18T512800BF-2.5 Datasheet - Page 20

HYB18T512800BF-2.5

Manufacturer Part Number

HYB18T512800BF-2.5

Description

IC DDR2 SDRAM 512MBIT 60TFBGA

Manufacturer

Qimonda

Datasheet

1.HYB18T512800BF-3.7.pdf

(58 pages)

Specifications of HYB18T512800BF-2.5

Format - Memory

RAM

Memory Type

DDR2 SDRAM

Memory Size

512M (64M x 8)

Speed

400MHz

Interface

Parallel

Voltage - Supply

1.7 V ~ 1.9 V

Operating Temperature

0°C ~ 95°C

Package / Case

60-TFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

675-1013-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

3.3

The Extended Mode Registers EMR(2) and EMR(3) are reserved for future use and must be programmed when setting the

mode register during initialization.

1) w = write only

2) When DRAM is operated at 85°C ≤

3) If PASR (Partial Array Self Refresh) is enabled, data located in areas of the array beyond the specified location will be lost if self refresh

Rev. 1.2, 2007-11

03292006-YBYM-WG0Z

Field

BA

A

SRF

A

DCC

Partial Self Refresh for 4 banks

PASR [2:0]

mode can be entered.

is entered. Data integrity will be maintained if

Bits

[15:14]

[13:8]

7

[6:4]

3

Type

w

w

w

w

w

w

Extended Mode Register EMR(2)

1)

Description

Bank Adress

00

01

10

11

Address Bus

Note: A13 is not available for 256 Mbit and x16 512 Mbit configuration

000000

Address Bus, High Temperature Self Refresh Rate for

0

1

Address Bus

000

Address Bus, Duty Cycle Correction (DCC)

0

1

Address Bus, Partial Array Self Refresh for 4 Banks

Note: Only for 256 Mbit and 512 Mbit components

000

001

010

011

100

101

110

111

B

B

B

B

B

B

B

B

T

B

B

B

B

B

B

B

B

B

Case

BA MRS

BA EMRS(1)

BA EMRS(2)

BA EMRS(3): Reserved

A7 disable

A7 enable

A Address bits

A3 DCC disabled

A3 DCC enabled

PASR0 Full Array

PASR1 Half Array (BA[1:0]=00, 01)

PASR2 Quarter Array (BA[1:0]=00)

PASR3 Not defined

PASR4 3/4 array (BA[1:0]=01, 10, 11)

PASR5 Half array (BA[1:0]=10, 11)

PASR6 Quarter array (BA[1:0]=11)

PASR7 Not defined

B

≤ 95°C the extended self refresh rate must be enabled by setting bit A7 to 1 before the self refresh

EMR(2) Programming Extended Mode Register Definition, BA

A Address bits

t

REF

conditions are met and no Self Refresh command is issued.

2)

20

512-Mbit Double-Data-Rate-Two SDRAM

2)

T

CASE

HYB18T512[40/80/16]0BF

> 85°C

Internet Data Sheet

TABLE 12

2:0

=010

B