SI3452MS8-KIT Silicon Laboratories Inc, SI3452MS8-KIT Datasheet - Page 17

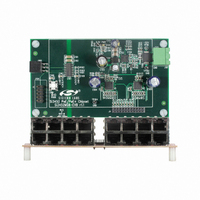

SI3452MS8-KIT

Manufacturer Part Number

SI3452MS8-KIT

Description

BOARD EVAL FOR SI3452

Manufacturer

Silicon Laboratories Inc

Type

Controllers & Processorsr

Specifications of SI3452MS8-KIT

Main Purpose

Special Purpose DC/DC, Power Over Ethernet

Board Type

Fully Populated

Utilized Ic / Part

Si3452

Interface Type

Ethernet, USB, I2C

Operating Voltage

3.3 V

Operating Temperature Range

- 40 C to + 85 C

Product

Modules

For Use With/related Products

Si3452

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Output

-

Voltage - Output

-

Voltage - Input

-

Power - Output

-

Frequency - Switching

-

Outputs And Type

-

Regulator Topology

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1836

5. Register Interface

The register types are described in the following sections. Refer to Table 19 on page 20 for a complete map of the

registers.

5.1. Interrupt (Registers 0x00–0x01)

An interrupt (INT pin low) is generated if any bit of the Interrupt register (register 0x00) is true. The Interrupt register

contains the information about which port is generating the interrupt or if the interrupt is due to a global event.

The port interrupt is generated by the port event register masked by the interrupt mask register.

Port event = (t

Rgood_CLS_mask) OR (DET_COMPL_EVENT AND DET_COMPL_MASK) OR (PwrGood_change AND

Pwrgood_change_MASK) OR (Penable_event AND Penable_mask)

The device event bit of the interrupt register is set if there is a change in the V

0x1D. Reading 0x1D clears the event.

5.2. Port Event (Registers 0x02–0x05)

This register contains bits that become true if the event has occurred. The registers are Clear On Read (COR) so

that reading these registers will clear the INT pin if the INT pin is being held low due to a port event.

5.3. Port Status (Registers 0x06–0x09)

These registers specify the port status. They are read-only registers.

The three class status bits indicate the last classification result for that port. If a classification has not been done or

if the port is shut down with no new classification result, the class status is reported as unknown.

The three detect status bits indicate the last detection result for that port. If a detection has not been done or if the

port is shut down with no new detection result, the detection status is reported as unknown.

t

tI

tI

shut down. Overload is defined as I>I

event. A tI

turning on. If the port is set to auto mode, it will attempt to re-power after >750 ms if there is a good detection

signature.

Rgood CLS indicates classification has been completed. Classification is only attempted after an Rgood; so, if

this bit is set, it indicates that detection gave an Rgood and classification is complete.

DET compl indicates the completion of a detection cycle. Normally, this bit will be masked. The DET complete

bit is used for legacy detection via modified link pulses. If the link pulse is returned indicating a PD is present,

then, normally, a detection is done, and the port is powered only if the result is not a short. In some cases, it

may be desirable to deny power to a port where an overload has been detected until the port is unplugged. In

this case, the Ropen result will be used to indicate the port has been unplugged and detection and classification

can resume.

Disconnect event indicates a disconnect has occurred. DC power was removed due to the dV/dt disconnect.

Overload conditions or loss of V

Pgood indicates the port has been turned on and did not shut down during the Tstart time.

Penable indicates a port has been turned on.

Pwr good indicates that the port has been turned on and the port voltage is within 2 V of V

Pwr Enable indicates the port has been turned on.

START

CUT

CUT

is an event bit indicating that an overload condition has existed for greater than 60 ms after the first 60 ms.

has a 16:1 up/down counter so that, if the overload is present at less than a 6.66% cycle, the port will not

is an event bit indicating an overload occurred for all but 5 ms of the initial 60 ms start up time.

CUT

START

event is also generated if the port is shutdown due to an overload or due to the protection clamp

Event AND t

START

EE

turns off ports but does not generate a disconnect event.

CUT

mask) OR (tI

or port voltage not within 2 V of V

Rev. 1.2

CUT

Event AND tI

CUT

mask) OR (Rgood_CLS_event AND

EE

EE

. The port is turned off on this

or temperature status in register

EE

.

Si3452

17