Z86CCP01ZEM Zilog, Z86CCP01ZEM Datasheet - Page 6

Z86CCP01ZEM

Manufacturer Part Number

Z86CCP01ZEM

Description

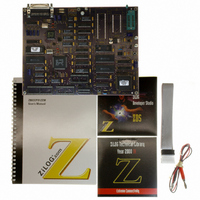

Z8 EMULATOR/PROGRAMMER BOARD

Manufacturer

Zilog

Series

Z8 OTPr

Type

In-Circuit Emulator Systemr

Datasheet

1.Z86CCP00ZAC.pdf

(8 pages)

Specifications of Z86CCP01ZEM

Contents

Circuit Board with Chips, Programming Sockets, Sockets with Target Cable, Interface Connector, Power Cable and Manual

For Use With/related Products

Zilog Z8® Series Microcontrollers

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-2002

Z86CCP00ZEM

Z86CCP00ZEM

PRECAUTIONS (Continued)

Z8® CCP™ In-Circuit Emulator

6. Ensure that the target cable is correctly aligned (pin-1

7. All Z8 control registers are Write-Only unless stated

8. The general-purpose registers after Power-On Reset

9. Power Supply ramp-up/rise time must be such that

10. If Program Counter jumps to an unknown address:

11. If the Program keeps resetting:

12. Check the T

6

to pin-1) before inserting into the target system.

Incorrect alignment may damage the emulator and/or

the target system.

otherwise.

or at initial emulator use will be different than the actual

device. The emulator self-test will always leave the

same values in the general-purpose registers, while

the real device will have a random or undefined value.

when the minimum power-on reset time (Tpor)

expires, the V

operating range of the device.

a. Stack is not set to internal. Register %F8 (P01M

b. Stack Pointer Register %FE(SPH) and Register

c. Any instruction other than “DI” was used to disable

d. The Stack overflowed into the general-purpose

e. Extra “POP”, “PUSH”. “IRET”, or “RET” was

f.

a. Program Counter rolled over from value “FFFF” to

b. Watch-Dog Timer (WDT) was not refreshed from

that you wish to emulate. The actual specification may

differ from the ICE chip specifications. The Z86C50

ICE chip typical WDT time period is configured using

bits 0 and 1 of the WDTMR register located in Bank F

of the Expanded Register Group at address 0FH.

Register) bit D2 not set to state “1”.

%FF(SPL) are not initialized. For internal Stack,

SPH does not have to be initialized since it is not

used. The SPH and SPL are reset to 00H after any

reset or Stop-Mode Recovery.

interrupts.

register locations.

encountered.

When making changes to the IMR register, the

GLOBAL interrupts must be disabled first using DI

instruction.

“0000” and proceeded back to beginning of

program.

devices with WDT feature.

POR

CC

and T

must be in the supported specified

WDT

specifications of the device

Note: Typical Z86C50 T

13. Do not start the emulator with OTP device in the

14. A shorted PLCC or DIP OTP can crash the emulator

15. The status color bar in OTP dialog box will be cleared

16. Do not press the emulator MASTER RESET when the

17. When device serialization is enabled in the OTP

18. The bits of non-implemented features (of devices

19. When interrupts are enabled, breakpointing after a

20. Port 0, Port 1, and Port 2 have auto latches

Typical Z86C50 ICE Chip WDT Time-Out Period

programming socket, as the emulator may not start up

correctly.

when inserted into the OTP programming socket. If a

PLCC part is inserted in such a way as to cause a

temporary short, then functionality is lost. An attempt

to perform BLANK CHECK on such a part will cause

the “hourglass” to appear continuously. The Windows

application must be reset and restarted.

in the area where a new window opens on top of it.

ICEBOX is in the OTP dialog for programming. If

MASTER RESET is pressed while the GUI is doing

OTP programming, close the OTP dialog box and

reopen it to reload the information back to the

hardware.

Command Status shows “Processing” after the GUI

re-establishes the communication link when “Retry”

was selected in the “Out of Synchronization with the

emulator” dialog box.

dialog, the GUI copies the current serial number to

code memory immediately before performing a

VERIFY operation. If this behavior is undesirable, then

device serialization should be disabled prior to

invoking the VERIFY operation.

having a PCON register) must be set to state “1” on the

emulator.

Halt instruction, the emulator will break at the first

instruction in the interrupt service routine that is

serviced when an interrupt occurs.

permanently enabled.

Note: The ICEBOX is really sitting idle, although the

Bit 1

0

0

1

1

Internal RC (ms) Time-Out

POR

Bit 0

= 6.0 ms.

0

1

0

1

CP97Z8X5301

Z86C50

18

75

4

9

Zilog