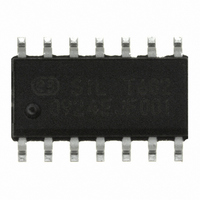

C8051T602-GS Silicon Laboratories Inc, C8051T602-GS Datasheet - Page 99

C8051T602-GS

Manufacturer Part Number

C8051T602-GS

Description

IC 8051 MCU 4K-EEPROM 14-SOIC

Manufacturer

Silicon Laboratories Inc

Series

C8051T60xr

Datasheet

1.C8051T600EDB.pdf

(188 pages)

Specifications of C8051T602-GS

Program Memory Type

OTP

Program Memory Size

4KB (4K x 8)

Package / Case

14-SOIC (3.9mm Width), 14-SOL

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051T6x

Core

8051

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

I2C/SMBus/UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

8

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051T600DK

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1404 - KIT DEV FOR C8051T60X MCU'S

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1655-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051T602-GS

Manufacturer:

Silicon Labs

Quantity:

135

The CRC calculation begins at address 0x0000 and ends at the end of user EPROM space. The EPBusy

bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete.

The 32-bit results will be available in the CRC3-0 registers. CRC3 is the MSB, and CRC0 is the LSB. The

polynomial used for the 32-bit CRC calculation is 0x04C11DB7.

Note: If a 16-bit CRC has been performed since the last device reset, a device reset should be initiated

before performing a 32-bit CRC operation.

20.3.2. Performing 16-bit CRCs on 256-Byte EPROM Blocks

A 16-bit CRC of individual 256-byte blocks of EPROM can be initiated by writing to the CRC0 byte over the

C2 interface. The value written to CRC0 is the high byte of the beginning address for the CRC. For exam-

ple, if CRC0 is written to 0x02, the CRC will be performed on the 256 bytes beginning at address 0x0200,

and ending at address 0x2FF. The EPBusy bit in register C2ADD will be set during the CRC operation, and

cleared once the operation is complete. The 16-bit results will be available in the CRC1-0 registers. CRC1

is the MSB, and CRC0 is the LSB. The polynomial for the 16-bit CRC calculation is 0x1021

20.3. Program Memory CRC

A CRC engine is included on-chip, which provides a means of verifying EPROM contents once the device

has been programmed. The CRC engine is available for EPROM verification even if the device is fully read

and write locked, allowing for verification of code contents at any time.

The CRC engine is operated through the C2 debug and programming interface, and performs 16-bit CRCs

on individual 256-byte blocks of program memory, or a 32-bit CRC the entire memory space. To prevent

hacking and extrapolation of security-locked source code, the CRC engine will only allow CRCs to be per-

formed on contiguous 256-byte blocks beginning on 256-byte boundaries (lowest 8-bits of address are

0x00). For example, the CRC engine can perform a CRC for locations 0x0400 through 0x04FF, but it can-

not perform a CRC for locations 0x0401 through 0x0500, or on block sizes smaller or larger than

256 bytes.

20.3.1. Performing 32-bit CRCs on Full EPROM Content

A 32-bit CRC on the entire EPROM space is initiated by writing to the CRC1 byte over the C2 interface.

Rev. 1.2

C8051T600/1/2/3/4/5/6

99