PIC12C508A/JW Microchip Technology, PIC12C508A/JW Datasheet - Page 19

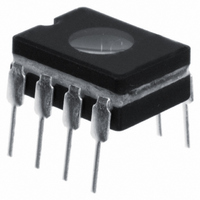

PIC12C508A/JW

Manufacturer Part Number

PIC12C508A/JW

Description

IC MCU EPROM 512X12 8CDIP

Manufacturer

Microchip Technology

Series

PIC® 12Cr

Datasheets

1.PIC12C508A-04SM.pdf

(113 pages)

2.PIC12C508A-04SM.pdf

(6 pages)

3.PIC12C508A-04SM.pdf

(16 pages)

4.PIC12C508A-04SM.pdf

(4 pages)

Specifications of PIC12C508A/JW

Core Processor

PIC

Core Size

8-Bit

Speed

4MHz

Peripherals

POR, WDT

Number Of I /o

5

Program Memory Size

768B (512 x 12)

Program Memory Type

EPROM, UV

Ram Size

25 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

8-CDIP (0.300", 7.62mm) Window

For Use With

ISPICR1 - ADAPTER IN-CIRCUIT PROGRAMMINGDVMCPA - KIT DVR BOARD EVAL SYSTEM MXDEV1DVA12XP080 - ADAPTER DEVICE FOR MPLAB-ICEAC124001 - MODULE SKT PROMATEII 8DIP/SOIC

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Data Converters

-

Connectivity

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PIC12C508A/JW

Manufacturer:

MICROCHIP

Quantity:

105

4.6

As a program instruction is executed, the Program

Counter (PC) will contain the address of the next

program instruction to be executed. The PC value is

increased by one every instruction cycle, unless an

instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided

by the GOTO instruction word. The PC Latch (PCL) is

mapped to PC<7:0>. Bit 5 of the STATUS register

provides page information to bit 9 of the PC (Figure 4-

8).

For a CALL instruction, or any instruction where the

PCL is the destination, bits 7:0 of the PC again are

provided by the instruction word. However, PC<8>

does not come from the instruction word, but is always

cleared (Figure 4-8).

Instructions where the PCL is the destination, or

Modify PCL instructions, include MOVWF PC, ADDWF

PC, and BSF PC,5.

FIGURE 4-8:

CALL or Modify PCL Instruction

GOTO Instruction

Note:

1999 Microchip Technology Inc.

PC

PC

Program Counter

11

11

Because PC<8> is cleared in the CALL

instruction, or any Modify PCL instruction,

all subroutine calls or computed jumps are

limited to the first 256 locations of any pro-

gram memory page (512 words long).

7

7

10

10

9

STATUS

9

LOADING OF PC

BRANCH INSTRUCTIONS -

PIC12C5XX

STATUS

PA0

Reset to ‘0’

PA0

8 7

8 7

Instruction Word

Instruction Word

PCL

PCL

0

0

0

0

4.6.1

The Program Counter is set upon a RESET, which

means that the PC addresses the last location in the

last page i.e., the oscillator calibration instruction. After

executing MOVLW XX, the PC will roll over to location

00h, and begin executing user code.

The STATUS register page preselect bits are cleared

upon a RESET, which means that page 0 is pre-

selected.

Therefore, upon a RESET, a

automatically cause the program to jump to page 0

until the value of the page bits is altered.

4.7

PIC12C5XX devices have a 12-bit wide L.I.F.O.

hardware push/pop stack.

A CALL instruction will push the current value of stack

1 into stack 2 and then push the current program

counter value, incremented by one, into stack level 1. If

more than two sequential CALL’s are executed, only

the most recent two return addresses are stored.

A RETLW instruction will pop the contents of stack level

1 into the program counter and then copy stack level 2

contents into level 1. If more than two sequential

RETLW’s are executed, the stack will be filled with the

address previously stored in level 2. Note that the

W register will be loaded with the literal value specified

in the instruction. This is particularly useful for the

implementation of data look-up tables within the

program memory.

Upon any reset, the contents of the stack remain

unchanged, however the program counter (PCL) will

also be reset to 0.

Note 1: There are no STATUS bits to indicate

Note 2: There are no instructions mnemonics

Stack

EFFECTS OF RESET

stack overflows or stack underflow condi-

tions.

called PUSH or POP. These are actions

that occur from the execution of the CALL

and RETLW instructions.

PIC12C5XX

GOTO instruction will

DS40139E-page 19