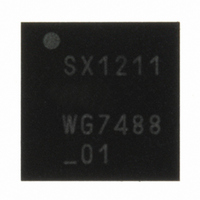

SX1211I084TRT Semtech, SX1211I084TRT Datasheet

SX1211I084TRT

Specifications of SX1211I084TRT

Available stocks

Related parts for SX1211I084TRT

SX1211I084TRT Summary of contents

Page 1

... European (ETSI EN 300-220 V2.1.1) and North American (FCC part 15.247 and 15.249) regulatory standards. Ordering Information Table 1: Ordering Information Part number Delivery SX1211I084TRT Tape & Reel SX1211I084T Tray TQFN-32 package – Operating range [-40;+85° refers to Lead Free packaging This device is WEEE and RoHS compliant ...

Page 2

... Reference Design Performance ........................................... 76 7.6.1. Sensitivity Flatness ........................................................... 77 7.6.2. Sensitivity vs. LO Drift....................................................... 78 7.6.3. Sensitivity vs. Receiver BW .............................................. 79 7.6.4. Sensitivity Stability over Temperature and Voltage............ 80 7.6.5. Sensitivity vs. Bit Rate ...................................................... 80 7.6.6. Adjacent Channel Rejection.............................................. 81 7.6.7. Output Power Flatness...................................................... 82 7.6.8. Pout and IDD vs. PA Setting ............................................. 83 Page SX1211 www.semtech.com ...

Page 3

... Figure 82: FSK - 1.56kbps - +/-33 kHz........................................ 87 Figure 83: FSK - 25 kbps - +/-50 kHz.......................................... 87 Figure 84: FSK - 40 kbps - +/-40 kHz.......................................... 87 Figure 85: DTS 6dB Bandwidth................................................... 88 Figure 86: DTS Power Spectral Density...................................... 88 Figure 87: IDD vs. Temp and VDD.............................................. 89 Figure 88: Package Outline Drawing........................................... 90 Figure 89: PCB Land Pattern...................................................... 90 Figure 90: Tape & Reel Dimensions ........................................... 91 Page SX1211 www.semtech.com ...

Page 4

... Phase-Locked Loop POR Power On Reset RBW Resolution BandWidth RF Radio Frequency RSSI Received Signal Strength Indicator Rx Receiver SAW Surface Acoustic Wave SPI Serial Peripheral Interface SR Shift Register Stby Standby Tx Transmitter uC Microcontroller VCO Voltage Controlled Oscillator XO Crystal Oscillator XOR eXclusive OR Page SX1211 www.semtech.com ...

Page 5

... ADVANCED COMMUNICATIONS & SENSING This product datasheet contains a detailed description of the SX1211 performance and functionality. Please consult the Semtech website for the latest updates or errata. 1. General Description The SX1211 is a single chip FSK and OOK transceiver capable of operation in the 863-870 MHz and 902-928 MHz license free ISM frequency bands, as well as the 950 - 960 MHz frequency band ...

Page 6

... ADVANCED COMMUNICATIONS & SENSING 1.2. Pin Diagram The following diagram shows the pins arrangement of the QFN package, top view. Notes: yyww refers to the date code ------ refers to the lot number nd Rev 7 – Sept 2 , 2008 Figure 2: SX1211 Pin Diagram Page SX1211 www.semtech.com ...

Page 7

... NRZ data input and output (Continuous mode) O Interrupt output O Interrupt output O PLL lock detection output I/O Connect to GND I/O Connect to GND VDD I Supply voltage O Regulated supply of the analog circuitry O Regulated supply of digital circuitry O Regulated supply of the PA I/O Connect to GND RFIO I/O RF input/output NC - Connect to GND Page SX1211 www.semtech.com ...

Page 8

... Crystal oscillator running Frequency synthesizer running Output power = +10 dBm (1) Output power = 1dBm Page SX1211 Min Max Unit -0.3 3.7 V -55 125 ° dBm Min Max Unit 2.1 3.6 V -40 +85 ° dBm Min Typ Max Unit - 0.1 2 µ µA - 1.3 1 3.0 3 www.semtech.com ...

Page 9

... Kb/s 50 200 kHz 12.8 15 MHz 2 - kHz 1 500 800 µs 180 - µs 200 - µs 250 - µs 260 - µs 290 - µs 320 - µs 340 - µs Typ Max Unit +12.5 - dBm -8.5 - dBm -112 - dBc/Hz - -47 dBc 120 500 µs 600 900 µs www.semtech.com ...

Page 10

... -101 - dBm - -113 - dBm - -106 - dBm - -111 - dBm - -105 - dBm - -12 - dBc - -48 - dBm - -37 - dBm - -33 - dBm - 250 kHz - 400 kHz - -28 - dBm - 280 500 µs - 600 900 µs - 400 - µs - 400 - µs - 460 - µs - 480 - µs - 520 - µs - 550 - µs - 600 - µ 1/Fdev www.semtech.com ...

Page 11

... NSS_DATA rising to falling edge. Note: on pin 10 (XTAL_P) and 11 (XTAL_N), maximum voltages of 1.8V can be applied. nd Rev 7 – Sept 2 , 2008 Conditions Min 0.8*VDD - Imax=1mA 0.9*VDD Imax=-1mA - - - 2 250 312 500 625 500 625 Page SX1211 Typ Max Unit - - V - 0.2*VDD 0.1*VDD MHz - 1 MHz - - µ www.semtech.com ...

Page 12

... Rev 7 – Sept 2 , 2008 I LO2 LO1 LO2 Tx Q RSSI LO2 Rx LO1 Generator Figure 3: SX1211 Detailed Block Diagram Page SX1211 Waveform generator OOK IRQ_0 demod IRQ_1 BitSync MOSI Control MISO FSK SCK demod NSS_CONFIG NSS_DATA CLKOUT DATA TEST(8:0) PLL_LOCK LO2 Rx LO1 Tx LO2 Tx www.semtech.com ...

Page 13

... Biasing digital blocks blocks VR_1V VR_DIG Pin 28 Pin 27 1ųF 220nF Y5V X7R Figure 4: Power Supply Breakdown Page Reg_VCO Reg_PA 0.85 V 1.80 V Biasing : Biasing : -VCO circuit -PA Driver -Ext. VCO -PA choke tank (ext) VR_PA VR_VCO Pin 3 Pin 29 100nF 47nF X7R X7R www.semtech.com SX1211 ...

Page 14

... Rev 7 – Sept 2 , 2008 ÷75.(P PFD ÷(R +1) i Fcomp LF_M XT_P Figure 5: Frequency Synthesizer Description ÷8 90° 90° ÷8 90° Figure 6: LO Generator Fcomp PLLBW 6 Page +1)+ Vtune LF_P VCO_P VCO_M VR_VCO LO1 Rx Receiver LOs I LO2 LO1 Tx Q Transmitter LOs I LO2 Tx Q www.semtech.com SX1211 ...

Page 15

... VCO voltage to be trimmed increments. Should the desired voltage range be inaccessible, the voltage may be adjusted further by changing the tank circuit inductance value. Note that an increase in inductance will result in an increase Vtune. nd Rev 7 – Sept 2 , 2008 915- 950- 928 960 Vtune ( mV ) 150 Page SX1211 www.semtech.com ...

Page 16

... Due to the manner in which the baseband OOK symbols are generated, the signal is always offset by the FSK frequency deviation (Fdev - as programmed in MCParam_Freq_dev). Hence, the center of the transmitted OOK signal is: nd Rev 7 – Sept 2 , 2008 RL1 LF_M CL2 CL1 LF_P Figure 7: Loop Filter 9 Frf , fsk Flo 8 9 Fxtal Frf , fsk Page SX1211 S www.semtech.com nd order ...

Page 17

... IF2. Note that from Section 3.4. recommended that IF2 be set to 100 kHz. nd Rev 7 – Sept 2 , 2008 9 Frf , ook , tx Flo Fdev 8 9 Fxtal Frf , ook , Frf , ook , rx Flo Fxtal Frf , ook , Page Fdev ) www.semtech.com SX1211 ...

Page 18

... Rev 7 – Sept 2 , 2008 First up-conversion Second up-conversion I LO2 LO1 LO2 Figure 8: Transmitter Architecture 1 Fdev Figure 9: I(t), Q(t) Overview ⇒ DATA ' ' ' 1 ' Frf Fdev ⇒ DATA ' ' ' ' 0 Frf Fdev Page SX1211 Interpolation DACs DDS filters Waveform generator Baseband I(t) Q(t) www.semtech.com Data Clock ...

Page 19

... Settings other than those programmable with a 12.8 MHz crystal can be obtained by selection of XTAL the correct reference oscillator frequency. Please contact your local Semtech representative for further details. 3.3.4. Fdev Setting in FSK Mode The frequency deviation, Fdev, of the FSK transmitter is programmed through bits MCParam_Freq_dev: For correct operation the modulation index ß ...

Page 20

... In OOK mode, the PA ramp times can be accurately controlled through the MCParam_PA_ramp register. Those bits directly control the slew rate of VR_PA output (pin 29). Table 11: PA Rise/Fall Times MCParam_PA_ramp t VR_PA 8 Rev 7 – Sept 2 , 2008 Fdev (rise / fall) PA_OUT 2 Page SX1211 www.semtech.com ...

Page 21

... VR_PA VR_PA PA Output power PA_OUT PA_OUT Figure 10: PA Control Figure 11: Optimal Load Impedance Chart Page SX1211 Pmax-1dB circle Pmax-1dB circle Pmax-1dB circle Pmax-1dB circle Max Power Max Power Max Power Max Power Zopt = 30+j25 Zopt = 30+j25 Zopt = 30+j25 Zopt = 30+j25 www.semtech.com ...

Page 22

... In receive mode, both PA and PA regulator are off and VR_PA is tied to ground. The external inductance LT1 is then used to bias the LNA. nd Rev 7 – Sept 2 , 2008 VR_PA 47nF 100nH SAW PA RFIO Low-pass and DC block VR_PA Reg_PA Rx_on PA RFIO To Antenna LNA Figure 13: Front-end Description Page SX1211 Antenna port DC block www.semtech.com ...

Page 23

... Figure 15: FSK Receiver Setting First down-conversion IF1 LO2 Rx Figure 16: OOK Receiver Setting Page SX1211 OOK demod Control logic -Pattern recognition Bit -FIFO handler synchronizer -SPI interface -Packet handler FSK demod th of the RF frequency Image Channel Frequencyl LO1 Rx frequency Image Channel Frequency LO1 Rx frequency www.semtech.com ...

Page 24

... Rev 7 – Sept 2 , 2008 ButterfFil t passive , filter Low-pass filter for FSK ( RXParam_PolyFilt_on=’’0’’ Polyphase filter for OOK ( RXParam_PolyFilt_on=’’1’’ ) the polyphase filter - Figure 17: Active Channel Filter Description Page ButterFilt f f requency C Canceled side of f requency www.semtech.com SX1211 ...

Page 25

... RXParam_ButterFilt. However, the whole receiver chain influences this cutoff frequency. Thus the channel select and resultant filter bandwidths are summarized in the following chart: nd Rev 7 – Sept 2 , 2008 Fdev FSK FSK drifts OOK Tbit fo 100 kHz RXParam _ PolypFilt " 0011 " OOK drifts Page SX1211 www.semtech.com ...

Page 26

... Butterworth Filter's BW, FSK 450 400 350 300 250 200 150 100 Val (RXParam_ButterFilt) [d] Figure 18: Butterworth Filter's Actual BW Polyphase Filter's BW, OOK 450 400 350 300 250 200 150 100 Val (RXParam_ButterFilt [d] RXParam_PolypFilt="0011" Figure 19: Polyphase Filter's Actual BW Page SX1211 Actual Theoretical Actual Theoretical www.semtech.com ...

Page 27

... IRQParam_Rx_stby_irq1. Figure 21 shows the timing diagram of the RSSI interrupt source, with IRQParam_RSSI_irq_thresh set to 28. nd Rev 7 – Sept 2 , 2008 RSSI Response -100 -80 -60 Pin [dBm] IF_Gain=00 IF_Gain=01 IF_Gain=10 Figure 20: RSSI Dynamic Range to the IRQ0 or IRQ1 Page -40 -20 0 IF_Gain=11 pins via bits IRQParam_Rx_stby_irq0 www.semtech.com SX1211 or ...

Page 28

... RXParam_OOK_thresh_type register. The recommended mode of operation is the “Peak” threshold mode, illustrated below in Figure 22: nd Rev 7 – Sept 2 , 2008 Clear interrupt Figure 21: RSSI IRQ Timings Fdev IF 2 100 kHz MCParam _ Freq _ dev " 00000011 2 * Fdev 2 BR Page SX1211 " www.semtech.com ...

Page 29

... MCParam_OOK_floor_thresh. nd Rev 7 – Sept 2 , 2008 Zoom Zoom Decay defined in RXPAram_OOK_thresh_step Period as defined in RXParam_OOK_thresh_dec_period Figure 22: OOK Demodulator Description Page SX1211 ‘’Peak -6dB’’ Threshold ‘’Floor’’ threshold defined by MCParam_OOK_floor_thresh Noise floor of receiver Time Fixed 6dB difference www.semtech.com ...

Page 30

... Rev 7 – Sept 2 , 2008 Set SX1211 in OOK Rx mode Adjust Bit Rate, Channel filter BW Default RXParam_OOK_thresh setting No input signal Continuous Mode Monitor DATA pin (pin 20) Increment MCParam_OOK_floor_thres Glitch activity on DATA ? Optimization complete Figure 23: Floor Threshold Optimization Page SX1211 www.semtech.com ...

Page 31

... The BitSync is automatically activated in Buffered and Packet modes. The bit synchronizer bit-rate is controlled by MCParam_BR. For a given bit rate, this parameter is determined by: nd Rev 7 – Sept 2 , 2008 ⇒ _ OOK _ cutoff 00 ⇒ _ OOK _ cutoff 11 output DATA mode DCLK IRQ_1 Figure 24: BitSync Description F XTAL MCParam Page Fcutoff Fcutoff www.semtech.com SX1211 ...

Page 32

... Bit Synchronizer and Active channel filter settings are a function of the reference oscillator crystal frequency, F Settings other than those programmable with a 12.8 MHz crystal can be obtained by selection of the correct reference oscillator frequency. Please contact your local Semtech representative for further details. 3.4.13. Data Output After OOK or FSK demodulation, the baseband signal is made available to the user on pin 20, DATA, when Continuous mode is selected ...

Page 33

... Input Input Input Input Input Input Input Input Input Input Output (1) Output Output Output (1) Output Output Input Output Input Output Output Output Output (2) Output (2) Output (2) Page SX1211 Comment NSS_CONFIG has the priority over NSS_DATA Output only if NSS_CONFIG or NSSDATA=’0’ www.semtech.com ...

Page 34

... The uC processing overhead is hence reduced further compared to Buffered mode. The maximum payload length is limited to the maximum FIFO limit of 64 bytes nd Rev 7 – Sept 2 , 2008 SX1211 CONTROL PACKET FIFO HANDLER (+SR) Page SX1211 DATA IRQ_0 IRQ_1 SPI CONFIG NSS_DATA SCK DATA MOSI MISO www.semtech.com ...

Page 35

... As described below, only one interface can be selected at a time with NSS_CONFIG having the priority: nd Rev 7 – Sept 2 , 2008 Continuous Buffered Packet NSS_CONFIG MOSI SPI MISO CONFIG SCK (slave) SPI DATA (slave) NSS_DATA Page SX1211 NSS_CONFIG MOSI MISO SCK NSS_DATA µ C (master) www.semtech.com ...

Page 36

... Config Data Config None A(0) stop D(7) D(6) D(5) D(4) D(3) D(2) D(1) D(0) Address = D(7) D(6) D(5) D(4) D(3) D(2) D(1) (In)/(Out) refers to SX1211 side Figure 27: Write Register Sequence Page New value at address A1 Current value at address A1* D(0) www.semtech.com SX1211 HZ (input) ...

Page 37

... D(7) D(6) D(5) D(4) D(3) D(2) D(1) Figure 28: Read Register Sequence byte written D1(3) D1(2) D1(1) D1(0) D2(7) D2(6) D2( (input) Figure 29: Write Bytes Sequence (ex: 2 bytes) Page SX1211 Current value at address byte written D2(4) D2(3) D2(2) D2(1) D2( www.semtech.com 16 x D(0) HZ (input (input) ...

Page 38

... D1(4) D1(3) D1(2) D1(1) D1(0) D2(7) D2(6) HZ (input) Figure 30: Read Bytes Sequence (ex: 2 bytes) byte1 byte0 8 SR (8bits) 1 MSB Figure 31: FIFO and Shift Register (SR) Page byte read D2(5) D2(4) D2(3) D2(2) D2(1) D2(0) FIFO LSB www.semtech.com SX1211 HZ (input) ...

Page 39

... B B+1 B & Stby Figure 32: FIFO Threshold IRQ Source Behavior Comments In Buffered mode, FIFO cannot be written in Stby before Tx In Packet mode, FIFO can be written in Stby before Tx In Packet & Buffered modes FIFO can be read in Stby after Rx Page SX1211 # of bytes in FIFO www.semtech.com ...

Page 40

... The packet handler is the block used in Packet mode. Its functionality is fully described in section 5.5. 5.2.5. Control The control block configures and controls the full chip’s behavior according to the settings programmed in the configuration registers. nd Rev 7 – Sept 2 , 2008 Bit N-1 = Bit N = Sync_value[1] Sync_value[0] Figure 33: Sync Word Recognition Page SX1211 www.semtech.com ...

Page 41

... The use of DCLK is compulsory in FSK and optional in OOK. DATA (NRZ) DCLK nd Rev 7 – Sept 2 , 2008 SX1211 CONTROL Figure 34: Continuous Mode Conceptual View T_DATA T_DATA Figure 35: Tx Processing in Continuous Mode Page SX1211 DATA IRQ_0 IRQ_1(DCLK) SPI NSS_CONFIG CONFIG SCK MOSI MISO www.semtech.com ...

Page 42

... The tables below give the description of the interrupts available in Continuous mode. Table 17: Interrupt Mapping in Continuous Rx Mode Note: In Continuous mode, no interrupt is available in Stby mode Table 18: Interrupt Mapping in Continuous Tx Mode nd Rev 7 – Sept 2 , 2008 Figure 36: Rx Processing in Continuous Mode Rx_stby_irq_0 Rx 00 (d) Sync IRQ_0 01 RSSI 1x - IRQ_1 DCLK Tx - IRQ_0 DCLK IRQ_1 Page SX1211 www.semtech.com ...

Page 43

... SCK MOSI MISO Figure 37: uC Connections in Continuous Mode Description Defines data operation mode ( X Defines IRQ_0 source in Rx mode X Enables Sync word recognition X Defines Sync word size X Defines the error tolerance on Sync word recognition X Defines Sync word value Page Continuous) www.semtech.com SX1211 ...

Page 44

... Tx mode after waiting at least 1 bit period from the last bit processed by modulator. nd Rev 7 – Sept 2 , 2008 SX1211 CONTROL FIFO (+SR) Figure 38: Buffered Mode Conceptual View Page SX1211 IRQ_0 IRQ_1 SPI NSS_CONFIG CONFIG NSS_DATA SCK DATA MOSI MISO www.semtech.com ...

Page 45

... Figure 40 illustrates an Rx processing with a 16 bytes FIFO size and Fifo_fill_method=0. Please note that in the illustrative example of section 5.4.6, the uC does not retrieve any byte from the FIFO through SPI Data, causing overrun. nd Rev 7 – Sept 2 , 2008 from SPI Data Page b10 b11 b12 b13 b14 b15 www.semtech.com SX1211 XXX ...

Page 46

... Table 21: Interrupt Mapping in Buffered Tx Mode nd Rev 7 – Sept 2 , 2008 Sync ( Write_byte 10 /Fifoempty 11 Sync 00 ( Fifofull 10 RSSI 11 Fifo_threshold /Fifoempty IRQ_0 Tx_irq_1=0 (d) Fifofull IRQ_1 Tx_irq_1=1 Tx_done Page b10 b11 b12 b13 b14 b15 b13 b12 b11 b10 Stby - - /Fifoempty - - Fifofull - Fifo_threshold Tx www.semtech.com SX1211 b16 b15 b14 ...

Page 47

... Defines IRQ_1 source in Rx & Stby modes X Defines IRQ_1 source in Tx mode X Defines FIFO filling method X Controls FIFO filling status X Defines Tx start condition and IRQ_0 source X Defines Sync word size X Defines the error tolerance on Sync word detection X Defines Sync word value Page SX1211 uC Description www.semtech.com ...

Page 48

... Wait for Fifo_threshold interrupt (i.e. Sync word has been detected and FIFO filled up to the defined threshold packet end Stby (SR’s content is lost). Read packet bytes from FIFO until /Fifoempty goes low (or correct number of bytes is read Sleep mode. nd Rev 7 – Sept 2 , 2008 Page SX1211 www.semtech.com ...

Page 49

... The length of the payload is set by the PKTParam_Payload_length register and is limited by the size of the FIFO selected. nd Rev 7 – Sept 2 , 2008 SX1211 CONTROL PACKET FIFO HANDLER (+SR) Figure 42: Packet Mode Conceptual View Page SX1211 IRQ_0 IRQ_1 SPI NSS_CONFIG CONFIG NSS_DATA SCK DATA MOSI MISO www.semtech.com ...

Page 50

... Optional Address byte (Node ID). Message data. Optional 2-bytes CRC checksum. nd Rev 7 – Sept 2 , 2008 Optional DC free data coding CRC checksum calculation Sync Word Address Message bytes byte 0 to (FIFO size) bytes Payload/FIFO Figure 43: Fixed Length Packet Format Page SX1211 CRC 2-bytes www.semtech.com ...

Page 51

... Payload_ready and CRC_OK interrupts (the latter only if CRC is enabled) can be generated to indicate the end of the packet reception. nd Rev 7 – Sept 2 , 2008 Optional DC free data coding CRC checksum calculation Length Sync Word Length Address Message 0 to (FIFO size - 1) bytes bytes byte byte Payload/FIFO Figure 44: Variable Length Packet Format Page SX1211 CRC 2-bytes www.semtech.com ...

Page 52

... In variable length Packet mode, PKTParam_Payload_length must be programmed with the maximum length permitted. If received length byte is smaller than this maximum then the packet is accepted and processed, otherwise it is discarded. nd Rev 7 – Sept 2 , 2008 can also be fully or partially Page SX1211 retrieved in Stby mode via www.semtech.com ...

Page 53

... The NRZ data is converted to Manchester code by coding ‘1’ as “10” and ‘0’ as “01”. In this case, the maximum chip rate is the maximum bit rate given in the specifications section and the actual bit rate is half the chip rate. nd Rev 7 – Sept 2 , 2008 CRC Polynomial = Figure 45: CRC Implementation Page www.semtech.com SX1211 0 X ...

Page 54

... Payload whitening/de-whitening is thus made transparent for the user, who still provides/retrieves NRZ data to/from the FIFO 5.5.7. Interrupt Signal Mapping Tables below give the description of the interrupts available in Packet mode. nd Rev 7 – Sept 2 , 2008 1/BR ...Sync Figure 46: Manchester Encoding/Decoding ran ata Figure 47: Data Whitening Page Payload... hite ata www.semtech.com SX1211 ... t ... ... 0 X ...

Page 55

... Rx 00 (d) Payload_ready 01 Write_byte 10 /Fifoempty 11 Sync or Adrs_match* 00 (d) CRC_OK 01 Fifofull 10 RSSI 11 Fifo_threshold Tx_start_irq_0=0 (d) Fifo_threshold Tx_start_irq_0=1 /Fifoempty Tx_irq_1=0 (d) Fifofull Tx_irq_1=1 Tx_done SX1211 IRQ_0 IRQ_1 NSS_CONFIG NSS_DATA SCK MOSI MISO Figure 48: uC Connections in Packet Mode Page SX1211 Stby - - /Fifoempty - - Fifofull - Fifo_threshold Tx uC www.semtech.com ...

Page 56

... Defines node address for Rx address filtering X X Defines packet format (fixed or variable length) X Defines the size of preamble to be transmitted X X Enables whitening/de-whitening process X X Enables CRC calculation/check X Enables and defines address filtering X Enables FIFO autoclear if CRC failed X X Defines FIFO access in Stby mode Page SX1211 www.semtech.com ...

Page 57

... FIFO. If the payload is read in Stby mode, then CRC_status is cleared when the user goes back to Rx mode and a new Sync word is detected. The Fifo_fill_method and Fifo_fill bits don’t have any meaning in the Packet mode and should be set to their default values only. nd Rev 7 – Sept 2 , 2008 Page SX1211 www.semtech.com ...

Page 58

... Selection between the two sets of frequency dividers of the PLL, Ri/Pi/Si r/w 0 R1/P1/S1 selected(d) 1 R2/P2/S2 selected Modulation type: r/w 01 OOK 10 FSK (d) r/w Data operation mode LSB (refer to Data_Mode_1 (Bit 2 Addr 1) OOK demodulator threshold type: 00 fixed threshold mode r/w 01 peak mode (d) 10 average mode 11 reserved Page SX1211 www.semtech.com ...

Page 59

... R2, P2, S2 generate 920.0 MHz in FSK mode Reserved r/w (d): “001” Ramp control of the rise and fall times of the Tx PA regulator output voltage in OOK mode: 00 3us r (d) Reserved r/w (d):”000” Page SX1211 Data Operation Mode Continuous (d) Buffered Packet www.semtech.com ...

Page 60

... Fifofull (d) 1 Tx_done Fifofull IRQ source r Goes high when FIFO is full. /Fifoempty IRQ source r Goes low when FIFO is empty r/w/ Goes high when an overrun error occurred. Writing a 1 clears flag and FIFO c r/w FIFO filling method (Buffered mode only): Page SX1211 www.semtech.com ...

Page 61

... Writing ‘1’ clears the bit PLL status: r/w/ 0 not locked c 1 locked Writing a ‘1’ clears the bit PLL_lock detect flag mapped to pin 23: r/w 0 Lock detect disabled, pin 23 is High-Z 1 Lock detect enabled(d) RSSI threshold for interrupt (coded as RSSI) (d): “00000000” Page SX1211 www.semtech.com ...

Page 62

... Sync word recognition: r/w 0 off ( Sync word size bits r bits 10 24 bits 11 32 bits (d) Number of errors tolerated in the Sync word recognition error (d) r error 10 2 errors 11 3 errors Reserved r/w (d):”0” Page SX1211 1 Val ( ButterFilt ) . 8 ( PolypFilt _ center ) 8 www.semtech.com ...

Page 63

... Reserved ≈ 32. π Description st r/w 1 Byte of Sync word (d): “00000000” nd Byte of Sync word (only used if Sync_size ≠ 00) 2 (d): “00000000” Byte of Sync word (only used if Sync_size = 1x) (d): “00000000” Byte of Sync word (only used if Sync_size = 11) (d): “00000000” Page SX1211 www.semtech.com ...

Page 64

... RW Description r/w Clkout control 0 Disabled 1 Enabled, Clk frequency set by Clkout_freq (d) r/w Frequency of the signal provided on CLKOUT: fclkout f if Clkout_freq = “00000” xtal f xtal fclkout 2 Clkout _ freq (d): 01111 (= 427 kHz) r/w Reserved (d): “00” Page SX1211 Val ( InterpFilt otherwise www.semtech.com ...

Page 65

... Node_adrs & 0x00 & 0xFF accepted, else rejected. r CRC check result for current packet (READ ONLY): 0 Fail 1 Pass r/w FIFO auto clear if CRC failed for current packet (d) 1 off r/w FIFO access in standby mode: 0 Write (d) 1 Read r/w Reserved (d): “000000” Page SX1211 www.semtech.com ...

Page 66

... GUI To aid the user with calculating appropriate R, P and S values, software is available to perform the frequency calculation. The SX1211 PLL frequency Calculator Software can be downloaded from the Semtech website. 7.2.2. .dll for Automatic Production Bench The Dynamically Linked Library (DLL) used by the software to perform these calculations is also provided, free of charge, to users, for inclusion in automatic production testing ...

Page 67

... Receiver is ready : -RSSI sampling is valid after a 1/Fdev period -Received data is valid Wait TS_FS Set SX1211 in Rx mode Wait for Receiver settling Set SX1211 in FS mode Wait for PLL settling Figure 49: Optimized Rx Cycle Page SX1211 Time SX1211 can be put in Any other mode www.semtech.com ...

Page 68

... TS_TR Data transmission can start in Continuous and Buffered modes Wait TS_FS Set SX1211 in Tx mode Packet mode starts its operation Set SX1211 in FS mode Wait for PLL settling Figure 50: Optimized Tx Cycle Page SX1211 Time SX1211 can be put in Any other mode www.semtech.com ...

Page 69

... IDDFS 1.3mA typ. Wait TS_TR Wait TS_HOP 1. Set R2/P2/S2 2. Set SX1211 in FS mode, change MCParam_Band if needed, then switch from R1/P1/S1 to R2/P2/S2 Figure 51: Tx Hop Cycle Page SX1211 Time SX1211 is now ready for data transmission Set SX1211 back in Tx mode www.semtech.com ...

Page 70

... IDDFS 1.3mA typ. Wait TS_RE SX1211 is now ready for data reception Wait TS_HOP 1. Set R2/P2/S2 2. Set SX1211 in FS mode, change MCParam_Band if needed, then switch from R1/P1/S1 to R2/P2/S2 Figure 52: Rx Hop Cycle Page SX1211 Time Set SX1211 back in Rx mode www.semtech.com ...

Page 71

... SX1211 mode nd Rev 7 – Sept 2 , 2008 IDD IDDT IDDR Wait TS_TR SX1211 is now ready for data transmission Set SX1211 in Tx mode Figure 53 Cycle Page Wait TS_RE SX1211 is ready to receive data Set SX1211 in Rx mode www.semtech.com SX1211 Time ...

Page 72

... Please note that while pin 13 is driven high, an over current consumption ten milliamps can be seen on VDD. nd Rev 7 – Sept 2 , 2008 Undefined Wait for Chip is ready from 10 ms this point on Figure 54: POR Timing Diagram Wait for > 100 High-Z ’’1’’ High-Z Figure 55: Manual Reset Timing Diagram Page SX1211 Chip is ready from this point on www.semtech.com ...

Page 73

... PCBs standard PCB technology (2 layers, 1.6mm, std via & clearance) => low cost Its performance is quasi-insensitive to dielectric thickness => minimal design effort to transfer to other PCB technologies (thickness layers, etc...) nd Rev 7 – Sept 2 , 2008 Figure 56: Reference Design Circuit Schematic Page SX1211 www.semtech.com ...

Page 74

... ADVANCED COMMUNICATIONS & SENSING The layers description is illustrated in Figure 57: The layout itself is illustrated in Figure 58. Please contact Semtech for gerber files. 9mm 7.5.3. Bill Of Material Table 35: Reference Design BOM Ref Value 868MHz 915MHz U1 SX1211 U2 869 MHz 915 MHz Q1 12.8 MHz 6 1uF C2 1uF ...

Page 75

... Ordering Information for Tools The modules described in section 7.5 can be ordered through your Semtech representative for evaluation purpose: Table 36: Tools Ordering Information Part Number Description SM1211E868 2 layer RF module, 868 MHz band SM1211E915 2 layer RF module, 915 MHz band ...

Page 76

... A0 125 nd Rev 7 – Sept 2 , 2008 Max. drift Programmed Actual kHz kHz +/- ppm 400 306 62 250 214 53 175 158 37 150 137 41 125 116 36 100 96 27 100 Max. drift Actual kHz +/- ppm 154 41 154 46 129 22 129 23 129 27 129 30 129 30 Page SX1211 www.semtech.com ...

Page 77

... Frequency [MHz] Sensitivity SAW Ripple Figure 62: Sensitivity Across the 915 MHz Band Page 14.0 12.0 10.0 8.0 6.0 4.0 2.0 0.0 -2.0 868 869 870 14.0 12.0 10.0 8.0 6.0 4.0 2.0 0.0 -2.0 920 922 924 926 928 www.semtech.com SX1211 ...

Page 78

... LO Drift [kHz] Figure 63: FSK Sensitivity Loss vs. LO Drift Sensitivity Loss vs. LO Drift 6.0 5.0 4.0 3.0 2.0 1.0 0.0 -1.0 -60 -40 - Drift [kHz] Figure 64: OOK Sensitivity Loss vs. LO Drift Page SX1211 100 www.semtech.com ...

Page 79

... Rev 7 – Sept 2 , 2008 Sensitivity vs. Fc 100 150 200 Fc of Active Filter [kHz] Figure 65: FSK Sensitivity vs Sensitivity Change vs. (Fc-Fo) 50 100 150 200 Fc-Fo [kHz] Figure 66: OOK Sensitivity Change vs Page SX1211 250 300 250 300 350 www.semtech.com ...

Page 80

... Rev 7 – Sept 2 , 2008 Sensitivity Stability 2.40 2.70 3.00 VDD [V] Figure 67: Sensitivity Stability Sensitivity Change over Bit Rate [kb/s] Figure 68: FSK Sensitivity vs. BR Page SX1211 3.30 3.60 85° C 25° C 0° C -40° 100 www.semtech.com ...

Page 81

... Rev 7 – Sept 2 , 2008 Sensitivity Change over the BR 4 6.5 9 11.5 Bit Rate [kbps] Figure 69: OOK Sensitivity vs. BR ACR in FSK Mode -600 -400 -200 0 200 Offset [kHz] Figure 70: ACR in FSK Mode Page SX1211 14 16.5 400 600 800 1000 www.semtech.com ...

Page 82

... Figure 71: ACR in OOK Mode Pout Over the Frequency Band 864 865 866 867 Frequency [MHz] Pout SAW Ripple Figure 72: Pout for 869 MHz Band Operation Page SX1211 100 200 300 4.0 2.0 0.0 -2.0 -4.0 -6.0 -8.0 868 869 870 www.semtech.com ...

Page 83

... SAW Ripple Figure 73: Pout for 915 MHz Band Operation Pout & IDD vs. TXParam_Pout Setting TXParam_Pout [d] Pout IDD Page SX1211 4.0 2.0 0.0 -2.0 -4.0 -6.0 -8.0 920 922 924 926 928 28.00 26.00 24.00 22.00 20.00 18.00 16.00 14.00 12.00 10. www.semtech.com ...

Page 84

... Rev 7 – Sept 2 , 2008 Pout & IDD vs. TXParam_Pout Setting TXParam_Pout [d] Pout IDD Pout Stability 2.4 2.7 3.0 VDD [V] Figure 76: Pout Stability Page SX1211 30.0 28.0 26.0 24.0 22.0 20.0 18.0 16.0 14.0 12.0 10 3.3 3.6 85° C 25° C -40° C 0° C www.semtech.com ...

Page 85

... ADVANCED COMMUNICATIONS & SENSING 7.6.10. Transmitter Spectral Purity nd Rev 7 – Sept 2 , 2008 Figure 77: 869 MHz Spectral Purity DC-1GHz Figure 78: 869 MHz Spectral Purity 1-6GHz Page SX1211 www.semtech.com ...

Page 86

... The OOK bit rate ranges form 1.56 to 16.7 kbps interesting to note that, for the lowest bit rates, a channel spacing approaching 200 kHz is achievable: Notes: The test conditions are: Fdev=100 kHz, TXParam_InterpFilt = 200 kHz nd Rev 7 – Sept 2 , 2008 Figure 79: OOK Spectrum - 2kbps Figure 80: OOK Spectrum - 8kbps Figure 81: OOK Spectrum - 16.7kbps Page SX1211 www.semtech.com ...

Page 87

... The default configuration of the SX1211 yields the bandwidth visible on Figure 83: Figure 84 shows the maximal bit rate and frequency deviation that can fit in the 868 to 868.6 MHz European sub- band: nd Rev 7 – Sept 2 , 2008 Figure 82: FSK - 1.56kbps - +/-33 kHz Figure 83: FSK - 25 kbps - +/-50 kHz Figure 84: FSK - 40 kbps - +/-40 kHz Page SX1211 www.semtech.com ...

Page 88

... BR=100 kbps (Chip rate=100kCps, as data whitening is enabled) Packet mode, data whitening enabled Note: Manchester encoding allows meeting an even lower power spectral density, at the expense of the bit rate efficiency. nd Rev 7 – Sept 2 , 2008 Figure 85: DTS 6dB Bandwidth Figure 86: DTS Power Spectral Density Page SX1211 www.semtech.com ...

Page 89

... Page SX1211 Standby Mode Current 2.4 2.7 3 3.3 VDD [V] Rx Mode Current 2.4 2.7 3 3.3 VDD [V] 85° C 25° C -40° C 0° C 3.3 3.6 www.semtech.com 85° C 25° C 0°C -40° C 3.6 85° C 25° C 0°C -40° C 3.6 ...

Page 90

... ADVANCED COMMUNICATIONS & SENSING 8. Packaging Information 8.1. Package Outline Drawing SX1211 is available in a 32-lead TQFN package as shown in Figure 88 below. 8.2. PCB Land Pattern nd Rev 7 – Sept 2 , 2008 Figure 88: Package Outline Drawing Figure 89: PCB Land Pattern Page SX1211 www.semtech.com ...

Page 91

... Rev 7 – Sept 2 , 2008 Direction of Feed Reel Reel Reel Ao/Bo Ko Size Width 5.25 1.10 330.2 12.4 +/-0.2 +/-0.1 Figure 90: Tape & Reel Dimensions Page SX1211 Min. Min.Trail QTY per Leader er Length Reel Length 400 400 3000 www.semtech.com ...

Page 92

... CUSTOMER’S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise. ...