MAX98088EWY+T Maxim Integrated Products, MAX98088EWY+T Datasheet

MAX98088EWY+T

Specifications of MAX98088EWY+T

Related parts for MAX98088EWY+T

MAX98088EWY+T Summary of contents

Page 1

... Automatic gain control (AGC) and a noise gate optimize the signal level of microphone input signals to make best use of the ADC dynamic range. The device is fully specified over the -40NC to +85NC extended temperature range. FlexSound is a trademark of Maxim Integrated Products, Inc. DIGITAL MICROPHONE LINEIN A1 LINEIN A2 + ...

Page 2

Stereo Audio Codec with FlexSound Technology General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 3

TABLE OF CONTENTS (continued) Record Path Signal Processing ...

Page 4

Stereo Audio Codec with FlexSound Technology TABLE OF CONTENTS (continued) Battery Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5

FlexSound Technology SDIN2 SDOUT2 LRCLK2 BCLK2 SDIN1 SDOUT1 LRCLK1 BCLK1 Stereo Audio Codec Functional Diagram 5 ...

Page 6

Stereo Audio Codec with FlexSound Technology ABSOLUTE MAXIMUM RATINGS (Voltages with respect to AGND.) DVDD, AVDD, HPVDD .........................................-0.3V to +2.2V SPKLVDD, SPKRVDD, DVDDS1, DVDDS2 ..........-0.3V to +6.0V DGND, HPGND, SPKLGND, SPKRGND ..............-0.1V to +0.1V HPVSS ............................... (HPGND - 2.2V) to ...

Page 7

ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( 2.2FF 1FF, ...

Page 8

Stereo Audio Codec with FlexSound Technology ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( ...

Page 9

ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( 2.2FF 1FF, ...

Page 10

Stereo Audio Codec with FlexSound Technology ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( ...

Page 11

ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( 2.2FF 1FF, ...

Page 12

Stereo Audio Codec with FlexSound Technology ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( ...

Page 13

ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( 2.2FF 1FF, ...

Page 14

Stereo Audio Codec with FlexSound Technology ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( ...

Page 15

ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( 2.2FF 1FF, ...

Page 16

Stereo Audio Codec with FlexSound Technology ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( ...

Page 17

ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( 2.2FF 1FF, ...

Page 18

Stereo Audio Codec with FlexSound Technology ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( ...

Page 19

ELECTRICAL CHARACTERISTICS (continued AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND. Line out loads ( 2.2FF 1FF, ...

Page 20

Stereo Audio Codec with FlexSound Technology DIGITAL INPUT/OUTPUT CHARACTERISTICS (continued AVDD HPVDD DVDD DVDDS1 (Note 1) PARAMETER SYMBOL BCLKS1, LRCLKS1, SDOUTS1—OUTPUT Output Low Voltage V OL Output High Voltage V OH Input Leakage ...

Page 21

DIGITAL INPUT/OUTPUT CHARACTERISTICS (continued AVDD HPVDD DVDD DVDDS1 (Note 1) PARAMETER SYMBOL DIGMICCLK—OUTPUT Output Low Voltage V OL Output High Voltage V OH INPUT CLOCK CHARACTERISTICS ( ...

Page 22

Stereo Audio Codec with FlexSound Technology AUDIO INTERFACE TIMING CHARACTERISTICS ( AVDD HPVDD DVDD DVDDS1 (Note 1) PARAMETER SYMBOL BCLK Cycle Time t BCLK High Time t BCLKH BCLK Low Time t BCLK or ...

Page 23

F BCLK (OUTPUT) t CLKSYNC LRCLK (OUTPUT) t CLKTX t HIZOUT SDOUT (OUTPUT) LSB HI-Z SDIN (INPUT) LSB MASTER MODE Figure 2. TDM Audio Interface Timing Diagram (TDM_ = 1, FSW_ = BCLK (OUTPUT) t ENDSYNC ...

Page 24

Stereo Audio Codec with FlexSound Technology Figure 4. Digital Microphone Timing Diagram TIMING CHARACTERSTICS ( AVDD HPVDD DVDD DVDDS1 (Note 1) PARAMETER SYMBOL Serial-Clock Frequency Bus Free Time Between STOP and ...

Page 25

TIMING CHARACTERISTICS (continued AVDD HPVDD DVDD DVDDS1 (Note 1) SDA t SU,DAT t LOW t SCL HIGH t HD,STA t R START CONDITION 2 Figure Interface Timing ...

Page 26

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 MODE DAC Playback 48kHz Stereo HP DAC ª HP 24-bit, music filters, 256Fs DAC Playback 48kHz Stereo HP DAC ª HP 24-bit, music ...

Page 27

AVDD PVDD DVDD DVDDS1 MODE DAC Playback 48kHz Mono SPK DAC ª SPK 24-bit, music filters Line Playback Mono SPK INA ª SPKL Differential inputs Full Duplex Full-Duplex 8kHz Mono RCV MIC1 ª ...

Page 28

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 29

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 30

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 31

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 32

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 33

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 34

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 35

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 36

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 37

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 38

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 39

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 40

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 41

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 42

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 43

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 44

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 45

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 46

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 47

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 48

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 49

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 50

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF ...

Page 51

AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R from HPL or HPR to HPGND 1FF +20dB, AV HPVSS MICPRE_ 0dB, AV ...

Page 52

Stereo Audio Codec with FlexSound Technology ( AVDD PVDD DVDD DVDDS1 between SPK_P and SPK_N. Receiver load (R HPL or HPR to HPGND REC = 1FF +20dB, ...

Page 53

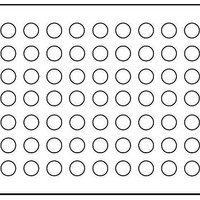

TOP VIEW (BUMP SIDE DOWN SPKRN SPKRGND SPKLVDD A SPKRN SPKRGND SPKLVDD B SPKRP SPKRP SPKRVDD C D BCLKS1 SDOUTS1 SPKRVDD E DVDDS1 MCLK N.C. DGND BCLKS2 LRCLKS2 F SDOUTS2 DVDDS2 SDINS2 G Stereo Audio Codec with ...

Page 54

Stereo Audio Codec with FlexSound Technology PIN NAME A1, B1 SPKRN A2, B2 SPKRGND A3, B3 SPKLVDD A4, B4 SPKLP A5, B5 SPKLN RECP/LOUTL/ A6 RXINP A7 PVDD A8 HPVSS A9 HPGND RECN/LOUTR/ B6 RXINN B7 C1P B8 C1N B9 ...

Page 55

PIN NAME Hardware Interrupt Output. IRQ can be programmed to pull low when bits in status register 0x00 change state. Read status register 0x00 to clear IRQ once set. Repeat faults have E5 IRQ no effect on IRQ until it ...

Page 56

Stereo Audio Codec with FlexSound Technology Detailed Description The MAX98088 is a fully integrated stereo audio codec with FlexSound technology and integrated amplifiers. Two differential microphone amplifiers can accept sig- nals from three analog inputs. One input can be retasked ...

Page 57

I 2 Configure the MAX98088 using the I IC uses a slave address of 0x20 or 00100000 for write operations and 0x21 or 00100001 for read operations. See the Serial Interface section for a complete inter- face ...

Page 58

Stereo Audio Codec with FlexSound Technology Table 1. Register Map (continued) REGISTER Time-Division SLOTL2 Multiplex Filters SRC Sample Rate Converter MIXERS DAC Mixer MIXDAL Left ADC Mixer Right ADC Mixer Left ...

Page 59

Table 1. Register Map (continued) REGISTER LEVEL CONTROL Sidetone DSTS 0 DAI1 Playback DV1M 0 Level DAI1 Playback Level DAI2 Playback DV2M 0 0 Level DAI2 Playback Level Left ADC 0 ...

Page 60

Stereo Audio Codec with FlexSound Technology Table 1. Register Map (continued) REGISTER Left Speaker Amplifier SPLM 0 0 Volume Control Right Speaker Amplifier SPRM 0 0 Volume Control MICROPHONE AGC Configuration AGCSRC AGCRLS Threshold ANTH SPEAKER SIGNAL ...

Page 61

Table 1. Register Map (continued) REGISTER DSP COEFFICIENTS EQ Band 1 (DAI1/DAI2) EQ Band 2 (DAI1/DAI2) EQ Band 3 (DAI1/DAI2) EQ Band 4 (DAI1/DAI2) Stereo Audio Codec with FlexSound Technology K_1[15:8] K_1[7:0] K1_1[15:8] ...

Page 62

Stereo Audio Codec with FlexSound Technology Table 1. Register Map (continued) REGISTER Band 5 (DAI1/DAI2) Excursion Limiter Biquad (DAI1/DAI2) REVISION ID Rev K_5[15:8] K_5[7:0] K1_5[15:8] K1_5[7:0] K2_5[15:8] K2_5[7:0] c1_5[15:8] c1_5[7:0] ...

Page 63

The IC includes comprehensive power management to allow the disabling of all unused circuits, minimizing supply current. Table 2. Power Management Registers REGISTER BIT NAME 7 SHDN 6 VBATEN 3 PERFMODE 2 HPPLYBCK 0x51 1 PWRSV8K 0 PWRSV 7 INAEN ...

Page 64

Stereo Audio Codec with FlexSound Technology Table 2. Power Management Registers (continued) REGISTER BIT NAME 7 HPLEN 6 HPREN 5 SPLEN 4 SPREN 0x4D 3 RECLEN 2 RECREN 1 DALEN 0 DAREN 7 BGEN 6 SPREGEN 0x4E 5 VCMEN 4 ...

Page 65

Microphone Inputs The device includes three differential microphone inputs and a low-noise microphone bias for powering the micro- phones (Figure 6). One microphone input can also be con- figured as a digital microphone input accepting signals from up to two ...

Page 66

Stereo Audio Codec with FlexSound Technology Table 3. Microphone Input Registers REGISTER BIT NAME 6 PA1EN/PA2EN 0x35/0x36 2 PGAM1/PGAM2 MICCLK 6 5 DIGMICL 0x48 4 DIGMICR 1 EXTMIC 0 66 DESCRIPTION MIC1/MIC2 Preamplifier Gain ...

Page 67

Table 3. Microphone Input Registers (continued) REGISTER BIT NAME 7 INABYP 4 MIC2BYP 0x4A 1 RECBYP 0 SPKBYP The device includes two sets of line inputs (Figure 7). Each set can be configured as a stereo single-ended input or as ...

Page 68

Stereo Audio Codec with FlexSound Technology Table 4. Line Input Registers REGISTER BIT NAME 6 INAEXT/INBEXT 2 0x37/0x38 1 PGAINA/PGAINB 0 7 INADIFF 0x47 6 INBDIFF ADC Input Mixers The IC’s stereo ADC accepts input from the microphone amplifiers, line ...

Page 69

Table 5. ADC Input Mixer Register REGISTER BIT NAME 0x23/0x24 MIXADL/MIXADR Record Path Signal Processing The device’s record signal path includes both automatic gain control (AGC) for the microphone inputs and a ...

Page 70

Stereo Audio Codec with FlexSound Technology Table 6. Record Path Signal Processing Registers REGISTER BIT NAME 0x01 3 AGC AGCSRC 6 0x3F 5 AGCRLS 4 70 DESCRIPTION Noise Gate Attenuation Reports ...

Page 71

Table 6. Record Path Signal Processing Registers (continued) REGISTER BIT NAME 3 AGCATK 2 0x3F 1 AGCHLD ANTH 5 4 0x40 3 2 AGCTH 1 0 Stereo Audio Codec with FlexSound Technology DESCRIPTION AGC Attack Time Defined ...

Page 72

Stereo Audio Codec with FlexSound Technology ATTACK TIME Figure 12. AGC Timing ADC Record Level Control The IC includes separate digital level control for the left and right ADC outputs (Figure 13). To optimize dynamic Figure 13. ADC Record Level ...

Page 73

Table 7. ADC Record Level Control Register REGISTER BIT NAME 5 AVLG/AVRG 4 3 0x33/0x34 2 AVL/AVR 1 0 Enable sidetone during full-duplex operation to add a low-level copy of the recorded audio signal to the play- back audio signal ...

Page 74

Stereo Audio Codec with FlexSound Technology Table 8. Sidetone Register REGISTER BIT NAME 7 DSTS 0x2E 2 DVST 1 0 Digital Audio Interfaces The IC includes two separate playback signal paths and one record signal path. Digital ...

Page 75

SDINS1 or SDINS2 to be routed from one interface to the other for output on SDOUTS2 or SDOUTS1. Both interfaces must be configured for the same sample rate, but the interface format need BCLKS1 LRCLKS1 SEL1 ...

Page 76

Stereo Audio Codec with FlexSound Technology Table 10. Digital Audio Interface Registers REGISTER BIT NAME 7 MAS1/MAS2 6 WCI1/WCI2 5 BCI1/BCI2 0x14/0x1C 4 DLY1/DLY2 2 TDM1/TDM2 1 FSW1/FSW2 0 WS1/WS2 76 DESCRIPTION DAI1/DAI2 Master Mode In master mode, DAI1/DAI2 outputs ...

Page 77

Table 10. Digital Audio Interface Registers (continued) REGISTER BIT NAME 7 OSR1 6 DAC_OSR1/ 5 DAC_OSR2 0x15/0x1D 2 BSEL1/ 1 BSEL2 0 7 SEL1/SEL2 6 5 LTEN1 0x16/0x1E LBEN1/ 4 LBEN2 DMONO1/ 3 DMONO2 Stereo Audio Codec with FlexSound Technology ...

Page 78

Stereo Audio Codec with FlexSound Technology Table 10. Digital Audio Interface Registers (continued) REGISTER BIT NAME HIZOFF1/ 2 HIZOFF2 0x16/0x1E SDOEN1/ 1 SDOEN2 SDIEN1/ 0 SDIEN2 7 SLOTL1/ SLOTL2 6 5 SLOTR1/ 0x17/0x1F SLOTR2 SLOTDLY1/ SLOTDLY2 1 ...

Page 79

WCI_ = 0, BCI_ = 0, DLY_ = 0, TDM_ = 0, FSW_ = 0, WS_ = 0, HIZOFF_ = 1, SLOTL_ = 0, SLOTR_ = 0 LRCLK SDOUT D15 D14 D13 D12 D11 D10 ...

Page 80

Stereo Audio Codec with FlexSound Technology WCI_ = 0, BCI_ = 1, DLY_ = 0, TDM_ = 1, FSW_ = 0, WS_ = 0, HIZOFF_ = 0, SLOTL_ = 0, SLOTR_ = 1 LRCLK SDOUT HI-Z L15 L14 L13 L12 ...

Page 81

The digital signal paths in the IC require a master clock (MCLK) between 10MHz and 60MHz to function. Internally, the MAX98088/MAX98089 requires a clock between 10MHz and 20MHz. A prescaler divides MCLK create the ...

Page 82

Stereo Audio Codec with FlexSound Technology Table 11. Clock Control Registers (continued) REGISTER BIT NAME 3 2 0x11 FREQ1 1 7 PLL1/PLL2 6 0x12/0x1A NI1/ NI2 0x13/0x1B 1 ...

Page 83

Table 11. Clock Control Registers (continued) REGISTER BIT NAME 7 6 DAI2_DAC_LP 5 4 0x4F 3 2 DAI1_DAC_LP DAC2DITHEN 2 DAC1DITHEN 0x50 1 CGM2_EN 0 CGM1_EN Stereo Audio Codec with FlexSound Technology DESCRIPTION DAI_ DAC Low Power ...

Page 84

Stereo Audio Codec with FlexSound Technology Table 12. Common NI1/NI2 Values PCLK (MHz) 8 11.025 12 10 13A9 1B18 1D7E 11 11E0 18A2 1ACF 11.2896 116A 1800 1A1F 1062 1694 1893 12 12.288 1000 160D 1800 13 0F20 14D8 16AF ...

Page 85

Table 13. Sample Rate Converter REGISTER BIT NAME 4 SRMIX_MODE 3 SRMIX_ENL 0x21 2 SRMIX_ENR 1 SRC_ENL 0 SRC_ENR Passband Filtering Each digital signal path in the IC includes options for defining the path bandwidth (Figure 19). The playback and ...

Page 86

Stereo Audio Codec with FlexSound Technology Table 14. Passband Filtering Registers REGISTER BIT NAME 7 MODE1 6 5 AVFLT1 4 0x18 3 DHF1 2 1 DVFLT1 0 3 DHF2 0x20 0 DCB2 86 DESCRIPTION DAI1 Passband Filtering Mode 0 = ...

Page 87

Table 15. Voice Highpass Filters AVFTL/DVFLT VALUE INTENDED SAMPLE RATE 000 001/011 16kHz/8kHz 010/100 16kHz/8kHz 101 8kHz to 48kHz 110/111 Stereo Audio Codec with FlexSound Technology N/A -10 -20 -30 -40 -50 -60 -10 -20 -30 -40 -50 -60 -10 ...

Page 88

Stereo Audio Codec with FlexSound Technology Playback Path Signal Processing The IC playback signal path includes automatic level control (ALC) and a 5-band parametric equalizer (EQ) (Figure 20). The DAI1 and DAI2 playback paths include separate ALCs controlled by a ...

Page 89

Table 16. Automatic Level Control Registers REGISTER BIT NAME 7 ALCEN 6 ALCRLS 5 4 0x43 3 ALCMB 2 1 ALCTH 0 Parametric Equalizer The parametric EQ contains five independent biquad filters with programmable gain, center frequency, and bandwidth. Each ...

Page 90

Stereo Audio Codec with FlexSound Technology Use the attenuator at the EQ’s input to avoid clipping the signal. The attenuator can be programmed for fixed attenuation or dynamic attenuation based on signal level. If the dynamic EQ clip detection is ...

Page 91

Playback Level Control The IC includes separate digital level control for the DAI1 and DAI2 playback audio paths. The DAI1 signal path Figure 23. Playback Level Control Block Diagram Table 18. DAC Playback Level Control Register REGISTER BIT NAME 7 ...

Page 92

Stereo Audio Codec with FlexSound Technology The IC’s stereo DAC accepts input from two digital audio paths. The DAC mixer routes any audio path to the left and right DACs (Figure 24). 5-BAND PARAMETRIC Figure 24. DAC Input Mixer Block ...

Page 93

The IC includes a single differential receiver amplifier. The receiver amplifier is designed to drive a 32I earpiece speaker. In cases where a single transducer is used for the loudspeaker and receiver, use the SPKBYP switch to route the receiver ...

Page 94

Stereo Audio Codecs with FlexSound Technology The IC’s receiver amplifier accepts input from the stereo DAC, the line inputs (single-ended or differential), and the MIC inputs. Configure the mixer to mix any combination of the available sources. When more than ...

Page 95

Receiver Output Volume Table 21. Receiver Output Level Register REGISTER BIT NAME RECLM/ 7 RECRM 4 3 0x3B/0x3C 2 RECVOLL/ RECVOLR 1 0 Stereo Audio Codecs with FlexSound Technology DESCRIPTION Receiver Output Mute 0 = Disabled 1 = Enabled Receiver ...

Page 96

Stereo Audio Codec with FlexSound Technology Speaker Amplifiers The IC integrates a stereo filterless Class D amplifier that offers much higher efficiency than Class AB without the typical disadvantages. The high efficiency of a Class D amplifier is due to ...

Page 97

The IC's speaker amplifiers accept input from the stereo DAC, the line inputs (single-ended ore differential), and the MIC inputs. Configure the mixer to mix any combination of the available sources. When more than one signal is selected, the mixer ...

Page 98

Stereo Audio Codec with FlexSound Technology Speaker Output Volume Table 23. Speaker Output Mixer Register REGISTER BIT NAME 7 SPLM/SPRM 4 3 0x3D/0x3E SPVOLL/SPVOLR 2 1 Speaker Amplifier Signal Processing The IC includes signal processing to improve the sound quality ...

Page 99

The transfer function for the user-programmable biquad is H( The coefficients ...

Page 100

Stereo Audio Codec with FlexSound Technology Table 24. Excursion Limiter Registers REGISTER BIT NAME 6 5 DHPUCF 4 0x41 1 DHPLCF 0 6 0x43 ALCRLS 0x42 DHPTH 1 0 100 DESCRIPTION Excursion Limiter Corner Frequency The ...

Page 101

The IC's power limiter tracks the RMS power delivered to the loudspeaker and briefly mutes the speaker amplifier output if the speaker is at risk of sustaining permanent damage. Loudspeakers are typically damaged when the voice coil overheats due to ...

Page 102

Stereo Audio Codec with FlexSound Technology Table 25. Power Limiter Registers (continued) REGISTER BIT NAME 7 6 PWRT2 5 4 0x45 3 2 PWRT1 1 0 The IC's distortion limiter ensures that the speaker amplifier’s output does not exceed the ...

Page 103

Table 26. Distortion Limiter Registers REGISTER BIT NAME 7 6 THDCLP 5 0x46 4 0 THDT1 DirectDrive Headphone Amplifier Traditional single-supply headphone amplifiers have outputs biased at a nominal DC voltage (typically half the supply). Large coupling capacitors are needed ...

Page 104

Stereo Audio Codec with FlexSound Technology CONVENTIONAL AMPLIFIER BIASING SCHEME DirectDrive AMPLIFIER BIASING SCHEME Figure 28. Traditional Amplifier Output vs. DirectDrive Output DACL DALEN DACR DAREN Figure 30. Headphone Amplifier Block Diagram 104 A Class H amplifier uses a Class ...

Page 105

Headphone Output Mixers The headphone amplifier mixer accepts input from the stereo DAC, the line inputs (single-ended or differen- tial), and the MIC inputs. Configure the mixer to mix any combination of the available sources. When more than Table 27. ...

Page 106

Stereo Audio Codec with FlexSound Technology Headphone Output Volume Table 28. Headphone Output Level Register REGISTER BIT NAME 7 HPLM/HPRM 4 3 0x39/0x3A HPVOLL/HPVOLR 106 DESCRIPTION Headphone Output Mute 0 = Disabled 1 = Enabled Left/Right Headphone ...

Page 107

Output Bypass Switches The IC's includes two output bypass switches that solve common applications problems. When a single trans- ducer is used for the loudspeaker and receiver, the need exists for two amplifiers to power the same transducer. Bypass switches ...

Page 108

Stereo Audio Codec with FlexSound Technology Click-and-Pop Reduction The IC includes extensive click-and-pop reduction cir- cuitry. The circuitry minimizes clicks and pops at turn-on, turn-off, and during volume changes. Zero-crossing detection is implemented on all analog PGAs and volume controls ...

Page 109

The IC features jack detection that can detect the inser- tion and removal of a jack as well as the load type. When a jack is detected, an interrupt on IRQ can be triggered to alert the microcontroller of the ...

Page 110

Stereo Audio Codec with FlexSound Technology Table 33. Jack Detection Registers REGISTER BIT NAME 0x02 6 JKSNS (Read Only) 7 JDETEN 1 0x4B JDEB 0 The IC measures the voltage applied to SPKLVDD (typically the battery voltage) and reports the ...

Page 111

The IC uses register 0x00 and IRQ to report the status of various device functions. The status register bits are set when their respective events occur, and cleared upon reading the register. Device status can be determined Table 35. Status ...

Page 112

Stereo Audio Codec with FlexSound Technology Device Revision Table 36. Device Revision Register REGISTER BIT NAME 0xFF REV (Read Only Serial Interface 2 The IC features C/SMBusK-compatible, ...

Page 113

The slave address is defined as the seven most signifi- cant bits (MSBs) followed by the read/write bit. For the IC, the seven most significant bits are 0010000. Setting the read/write bit to 1 (slave address = 0x21) configures the ...

Page 114

Stereo Audio Codec with FlexSound Technology The slave address with the R/W bit set to 0 indicates that the master intends to write data to the ICs. The ICs acknowledge receipt of the address byte during the master-generated 9th SCL ...

Page 115

Figures 39 and 40 provide example operating circuits for the ICs. sThe external components shown are the minimum required for the ICs to operate. Additional components may be required by the application. TO MICROCONTROLLER 10MHz TO 60MHz CLOCK INPUT DIGITAL ...

Page 116

Stereo Audio Codec with FlexSound Technology 10kI TO MICROCONTROLLER 10MHz TO 60MHz CLOCK INPUT DIGITAL AUDIO PORT CONTROL PORT DATA DIGITAL MIC 1 CLOCK DATA DIGITAL MIC 2 CLOCK 2.2kI JACKSNS HEADSET MICROPHONE LINE INPUT LINE ...

Page 117

Filterless Class D Operation Traditional Class D amplifiers require an output filter to recover the audio signal from the amplifier’s output. The filters add cost, increase the solution size of the amplifier, and can decrease efficiency and THD+N performance. The ...

Page 118

Stereo Audio Codec with FlexSound Technology Many configuration options in the ICs can be made while the devices are operating, however, some regis- ters should only be adjusted when the corresponding audio path is disabled. Table 38 lists the registers ...

Page 119

Charge-Pump Flying Capacitor The value of the flying capacitor (connected between C1N and C1P) affects the output resistance of the charge pump. A value that is too small degrades the device’s ability to provide sufficient current drive, which leads to ...

Page 120

Stereo Audio Codec with FlexSound Technology Recommended PCB Routing The IC uses a 63-bump WLP package. Figure 42 provides an example of how to connect to all active bumps using 3 layers of the PCB. To ensure uninter- rupted ground ...

Page 121

Route microphone signals from the microphone to the ICs as a differential pair, ensuring that the positive and negative signals follow the same path as closely as pos- sible with equal trace length. When using single-ended microphones or other single-ended ...

Page 122

Stereo Audio Codec with FlexSound Technology For the latest package outline information and land patterns www.maxim-ic.com/packages. Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix ...

Page 123

... Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 2010 Maxim Integrated Products © ...