CY7C1315BV18-200BZC Cypress Semiconductor Corp, CY7C1315BV18-200BZC Datasheet - Page 22

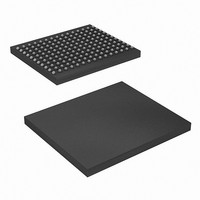

CY7C1315BV18-200BZC

Manufacturer Part Number

CY7C1315BV18-200BZC

Description

SRAM (Static RAM)

Manufacturer

Cypress Semiconductor Corp

Datasheet

1.CY7C1313BV18-167BZC.pdf

(28 pages)

Specifications of CY7C1315BV18-200BZC

Format - Memory

RAM

Memory Type

SRAM - Synchronous, QDR II

Memory Size

18M (512K x 36)

Speed

200MHz

Interface

Parallel

Voltage - Supply

1.7 V ~ 1.9 V

Operating Temperature

0°C ~ 70°C

Package / Case

165-LFBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C1315BV18-200BZC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document Number: 38-05620 Rev. *C

Switching Characteristics

t

t

t

t

t

t

Set-up Times

t

t

t

t

Hold Times

t

t

t

t

Output Times

t

t

t

Notes:

Parameter

25. This part has a voltage regulator internally; t

26. All devices can operate at clock frequencies as low as 119 MHz. When a part with a maximum frequency above 167 MHz is operating at a lower clock frequency,

27. For D2 data signal on CY7C1911BV18 device, t

POWER

CYC

KH

KL

KHKH

KHCH

SA

SC

SCDDR

SD

HA

HC

HCDDR

HD

CO

DOH

CCQO

Cypress

can be initiated.

it requires the input timings of the frequency range in which it is being operated and will output data with the output timings of that frequency range.

[27]

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

Consortium

KHKH

KHKL

KLKH

KHKH

KHCH

AVKH

IVKH

IVKH

DVKH

KHAX

KHIX

KHIX

KHDX

CHQV

CHQX

CHCQV

Parameter

V

Access

K Clock and C Clock Cycle

Time

Input Clock (K/K; C/C)

HIGH

Input Clock (K/K; C/C)

LOW

K Clock Rise to K Clock

Rise and C to C Rise

(rising edge to rising edge)

K/K Clock Rise to C/C

Clock Rise (rising edge to

rising edge)

Address Set-up to K Clock

Rise

Control Set-up to K Clock

Rise (RPS, WPS)

Double Data Rate Control

Set-up to Clock (K, K) Rise

(BWS

BWS

D

(K/K) Rise

Address Hold after K

Clock Rise

Control Hold after K Clock

Rise (RPS, WPS)

Double Data Rate Control

Hold after Clock (K, K)

Rise (BWS

BWS

D

(K/K) Rise

C/C Clock Rise (or K/K in

single clock mode) to Data

Valid

Data Output Hold after

Output C/C Clock Rise

(Active to Active)

C/C Clock Rise to Echo

Clock Valid

DD

[X:0]

[X:0]

(Typical) to the First

3

2

0

Set-up to Clock

Hold after Clock

)

, BWS

Description

, BWS

[25]

Over the Operating Range

POWER

0

, BWS

3

1,

)

SD

BWS

is the time that the power needs to be supplied above V

is 0.5 ns for 200 MHz, 250 MHz, 278 MHz and 300 MHz frequencies.

1,

2

,

–0.45

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

3.30 5.25 3.60 5.25

1.32

1.32

1.49

0.0

0.4

0.4

0.3

0.3

0.4

0.4

0.3

0.3

300 MHz

1

–

[24,26]

1.45

0.45

0.45

–

–

–

–

–

–

–

–

–

–

–

–

–0.45

1.4

1.4

1.6

0.0

0.4

0.4

0.3

0.3

0.4

0.4

0.3

0.3

278 MHz

1

–

1.55

0.45

0.45

–

–

–

–

–

–

–

–

–

–

–

–

–0.45

0.35

0.35

0.35

0.35

4.0

1.6

1.6

1.8

0.0

0.5

0.5

0.5

0.5

250 MHz

1

–

–

DD

5.25

0.45

0.45

1.8

minimum initially before a Read or Write operation

–

–

–

–

–

–

–

–

–

–

–

–

–0.45

200 MHz

5.0

2.0

2.0

2.2

0.0

0.6

0.6

0.4

0.4

0.6

0.6

0.4

0.4

1

–

–

CY7C1313BV18

CY7C1315BV18

CY7C1311BV18

CY7C1911BV18

0.45

0.45

6.3

2.2

–

–

–

–

–

–

–

–

–

–

–

–0.50

167 MHz

6.0

2.4

2.4

2.7

0.0

0.7

0.7

0.5

0.5

0.7

0.7

0.5

0.5

1

–

–

Page 22 of 28

0.50

0.50

8.4

2.7

–

–

–

–

–

–

–

–

–

–

–

–

Unit

ms

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

[+] Feedback