NTD25P03LG ON Semiconductor, NTD25P03LG Datasheet - Page 4

NTD25P03LG

Manufacturer Part Number

NTD25P03LG

Description

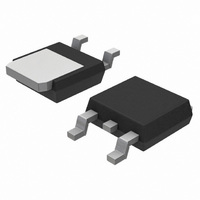

MOSFET P-CH 30V 25A DPAK

Manufacturer

ON Semiconductor

Type

Power MOSFETr

Datasheet

1.NTD25P03LT4G.pdf

(9 pages)

Specifications of NTD25P03LG

Fet Type

MOSFET P-Channel, Metal Oxide

Fet Feature

Logic Level Gate

Rds On (max) @ Id, Vgs

80 mOhm @ 25A, 5V

Drain To Source Voltage (vdss)

30V

Current - Continuous Drain (id) @ 25° C

25A

Vgs(th) (max) @ Id

2V @ 250µA

Gate Charge (qg) @ Vgs

20nC @ 5V

Input Capacitance (ciss) @ Vds

1260pF @ 25V

Power - Max

75W

Mounting Type

Surface Mount

Package / Case

DPak, TO-252 (2 leads+tab), SC-63

Configuration

Single

Transistor Polarity

P-Channel

Resistance Drain-source Rds (on)

0.08 Ohm @ 5 V

Forward Transconductance Gfs (max / Min)

13 S

Drain-source Breakdown Voltage

30 V

Gate-source Breakdown Voltage

+/- 15 V

Continuous Drain Current

25 A

Power Dissipation

75000 mW

Maximum Operating Temperature

+ 150 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 55 C

Number Of Elements

1

Polarity

P

Channel Mode

Enhancement

Drain-source On-res

0.08Ohm

Drain-source On-volt

30V

Gate-source Voltage (max)

±15V

Operating Temp Range

-55C to 150C

Operating Temperature Classification

Military

Mounting

Surface Mount

Pin Count

2 +Tab

Package Type

DPAK

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

NTD25P03LG

NTD25P03LGOS

NTD25P03LGOS

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

NTD25P03LG

Manufacturer:

ON

Quantity:

5 025

Company:

Part Number:

NTD25P03LG

Manufacturer:

ON

Quantity:

12 500

Company:

Part Number:

NTD25P03LG

Manufacturer:

ON

Quantity:

12 500

by recognizing that the power MOSFET is charge

controlled. The lengths of various switching intervals (Dt)

are determined by how fast the FET input capacitance can

be charged by current from the generator.

The published capacitance data is difficult to use for

calculating rise and fall because drain−gate capacitance

varies greatly with applied voltage. Accordingly, gate

charge data is used. In most cases, a satisfactory estimate of

average input current (I

rudimentary analysis of the drive circuit so that

t = Q/I

During the rise and fall time interval when switching a

resistive load, V

known as the plateau voltage, V

times may be approximated by the following:

t

t

where

V

R

and Q

During the turn−on and turn−off delay times, gate current is

not constant. The simplest calculation uses appropriate

values from the capacitance curves in a standard equation for

voltage change in an RC network. The equations are:

t

t

r

f

d(on)

d(off)

GG

G

= Q

= Q

Switching behavior is most easily modeled and predicted

= the gate drive resistance

= the gate drive voltage, which varies from zero to V

= R

2

2

= R

2

G(AV)

x R

x R

and V

G

G

G

G

C

C

/(V

/V

iss

iss

GSP

GSP

GG

In [V

In (V

GS

are read from the gate charge curve.

− V

remains virtually constant at a level

GG

GG

GSP

/(V

/V

)

G(AV)

GSP

GG

)

− V

2200

2000

1800

1600

1400

1200

1000

SGP

) can be made from a

800

600

400

200

GSP

0

. Therefore, rise and fall

10

)]

C

C

iss

rss

−V

GATE−TO−SOURCE OR DRAIN−TO−SOURCE

V

GS

POWER MOSFET SWITCHING

5

DS

Figure 7. Capacitance Variation

= 0 V

0

http://onsemi.com

V

GS

VOLTAGE (VOLTS)

GG

= 0 V

−V

5

DS

4

The capacitance (C

a voltage corresponding to the off−state condition when

calculating t

on−state when calculating t

complicate the analysis. The inductance of the MOSFET

source lead, inside the package and in the circuit wiring

which is common to both the drain and gate current paths,

produces a voltage at the source which reduces the gate drive

current. The voltage is determined by Ldi/dt, but since di/dt

is a function of drain current, the mathematical solution is

complex.

complicates the mathematics. And finally, MOSFETs have

finite internal gate resistance which effectively adds to the

resistance of the driving source, but the internal resistance

is difficult to measure and, consequently, is not specified.

resistance (Figure 9) shows how typical switching

performance is affected by the parasitic circuit elements. If

the parasitics were not present, the slope of the curves would

maintain a value of unity regardless of the switching speed.

The circuit used to obtain the data is constructed to minimize

common inductance in the drain and gate circuit loops and

is believed readily achievable with board mounted

components. Most power electronic loads are inductive; the

data in the figure is taken with a resistive load, which

approximates an optimally snubbed inductive load. Power

MOSFETs may be safely operated into an inductive load;

however, snubbing reduces switching losses.

10

At high switching speeds, parasitic circuit elements

The resistive switching time variation versus gate

15

C

C

C

oss

rss

iss

T

d(on)

The

J

= 25°C

20

and is read at a voltage corresponding to the

MOSFET

iss

) is read from the capacitance curve at

25

d(off)

output

.

capacitance

also