XC9572XV-5PC44C Xilinx Inc, XC9572XV-5PC44C Datasheet

XC9572XV-5PC44C

Specifications of XC9572XV-5PC44C

Available stocks

Related parts for XC9572XV-5PC44C

XC9572XV-5PC44C Summary of contents

Page 1

R DS049 (v3.0) June 25, 2007 Note: This product is being discontinued. You cannot order parts in this family after May 14, 2008. Xilinx recom- mends replacing XC9500XV devices with equivalent XC9500XL devices in all designs as soon as possible. ...

Page 2

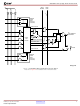

... Registers T (ns (ns For each FB outputs (depending on package pin-count) and associated output enable signals drive directly to the IOBs. See . JTAG Controller I/O Blocks Figure 1: XC9500XV Architecture XC9536XV XC9572XV 36 72 800 1,600 3.5 3.5 www.xilinx.com Figure 1. In-System Programming Controller 54 Function Block 1 18 Macrocells ...

Page 3

... The FB generates 18 outputs that drive the Fast CONNECT II switch matrix. These 18 outputs and their corresponding output enable signals also drive the IOB. DS049 (v3.0) June 25, 2007 Product Specification XC9536XV XC9572XV 3.5 3.5 222 222 1 1 XC9536XV XC9572XV Xilinx Packaging for more information ...

Page 4

XC9500XV Family High-Performance CPLD From 54 Fast CONNECT II Switch Matrix Macrocell Each XC9500XV macrocell may be individually configured for a combinatorial or registered function. The macrocell and associated FB logic is shown in Five direct product terms from the ...

Page 5

R 54 Allocator Figure 3: XC9500XV Macrocell Within Function Block Note: See DS049 (v3.0) June 25, 2007 Product Specification Global Global Set/Reset Clocks 3 Additional Product Terms (from other macrocells) Product Term Set 1 0 Product Term Product Term Clock ...

Page 6

XC9500XV Family High-Performance CPLD All global control signals are available to each individual macrocell, including clock, set/reset, and output enable sig- nals. As shown in Figure 4, the macrocell register clock originates from either of three global clocks or a ...

Page 7

R Product Term Allocator The product term allocator controls how the five direct prod- uct terms are assigned to each macrocell. For example, all five direct terms can drive the OR function as shown in Figure 5. Product Term Allocator ...

Page 8

XC9500XV Family High-Performance CPLD The product term allocator can re-assign product terms from any macrocell within the FB by combining partial sums of products over several macrocells, as shown in In this example, the incremental delay is only 2 product ...

Page 9

R The internal logic of the product term allocator is shown in Figure 8. From Upper Macrocell From Lower Macrocell DS049 (v3.0) June 25, 2007 Product Specification To Upper Macrocell Product Term Allocator To Lower Macrocell Figure 8: Product Term ...

Page 10

XC9500XV Family High-Performance CPLD Fast CONNECT II Switch Matrix The Fast CONNECT II Switch Matrix connects signals to the FB inputs, as shown in Figure 9. All IOB outputs (corre- sponding to user pin inputs) and all FB outputs drive ...

Page 11

R I/O Block The I/O Block (IOB) interfaces between the internal logic and the device user I/O pins. Each IOB includes an input buffer, output driver, output enable selection multiplexer, To Fast CONNECT II Switch Matrix Macrocell (Inversion in AND-array) ...

Page 12

XC9500XV Family High-Performance CPLD The input buffer is compatible with 3.3V CMOS and 2.5V CMOS signals. The input buffer uses the internal 2.5V volt- age supply ( ensure that the input thresholds are CCINT constant and do not ...

Page 13

R Output Voltage V CCIO Standard T SLEW 1.2V 0 (a) Figure 12: Output Slew-Rate Control For (a) Rising and (b) Falling Outputs Set to PIN during valid user operation Drive to V Level CCIO 0 PIN Figure 13: Bus-Hold ...

Page 14

XC9500XV Family High-Performance CPLD Mixed Voltage The I/Os on each XC9500XV device are fully 3.3V tolerant even though the core power supply is 2.5V. This allows 3.3V CMOS signals to connect directly to the XC9500XV inputs without damage. In addition, ...

Page 15

R Design Security XC9500XV devices incorporate advanced data security fea- tures which fully protect the programming data against unauthorized reading or inadvertent device erasure/repro- gramming. Table 3 shows the four different security settings available. The read security bits can be ...

Page 16

XC9500XV Family High-Performance CPLD Combinatorial Logic Propagation Delay = T (a) T PSU Combinatorial Logic P-Term Clock Path Setup Time = T PSU (c) Table 4: Timing Model Parameters Description Propagation Delay Global Clock Setup Time Global Clock-to-output Product Term ...

Page 17

GCK T GSR T GTS Power-Up Characteristics The XC9500XV devices are well behaved under all operat- ing conditions. During power-up each XC9500XV device employs internal circuitry which keeps the device in the qui- escent state until ...

Page 18

XC9500XV Family High-Performance CPLD Power-Up Guidelines Figure 19 shows a block diagram of the internal configura- tion controller, which transfers the EPROM bits to the latches. Some important things to note are: • The V is sensed to determine when ...

Page 19

R Revision History The following table shows the revision history for this document. Date Version 01/19/99 1.0 Initial Xilinx release. Advance Information Specification. 06/12/00 1.1 Updated 3.3V information, added Output Banking, added DS049 number. Added WebPACK information and minor edits. ...