IDT71V433 Integrated Device Technology, Inc., IDT71V433 Datasheet

IDT71V433

Available stocks

Related parts for IDT71V433

IDT71V433 Summary of contents

Page 1

... The burst mode feature offers the highest level of performance to the system designer, as the IDT71V433 can provide four cycles of data for a single address presented to the SRAM. An internal burst address counter accepts the first cycle address from the processor, initiating the access sequence ...

Page 2

... NC pins are not electrically connected to the chip. I HIGH Asynchronous sleep mode input. ZZ HIGH will gate the CLK internally and power down the IDT71V433 to its lowe st power consumption level. Data retention is guaranteed in Sleep Mode. ZZ has an internal pull-down resistor. 2 Commercial and Industrial Temperature Ranges – ...

Page 3

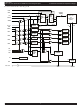

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs LBO ADV CLK ADSC ADSP A – BWE Powerdown OE 32 I/O –I Commercial and Industrial Temperature Ranges Burst CE Sequence 2 Burst Binary Logic Counter Q0 CLR Q1 2 CLK ADDRESS REGISTER 15 Byte 1 Write Register Byte 2 Write Register ...

Page 4

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Symbol Rating (2) V Terminal Voltage with TERM Respect to GND (3) V Terminal Voltage with TERM Respect to GND T Operating Temperature A T Temperature Under Bias BIAS T Storage Temperature STG P Power Dissipation Output Current OUT NOTES: 1 ...

Page 5

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs 100 I I DDQ V 5 SSQ SSQ V 11 DDQ DDQ V 21 SSQ SSQ V 27 DDQ I I NOTES 1. Pin 14 does not have to be directly connected Pin 64 can be left unconnected and the device will always remain in active mode. ...

Page 6

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Address Operation Deselected Cycle, Power Down Deselected Cycle, Power Down Deselected Cycle, Power Down Deselected Cycle, Power Down Deselected Cycle, Power Down Read Cycle, Begin Burst Read Cycle, Begin Burst Read Cycle, Begin Burst ...

Page 7

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs GW Operation Read H Read H Write all Bytes L Write all Bytes H (2) Write Byte 1 H (2) Write Byte 2 H (2) Write Byte 3 H (2) Write Byte 4 H NOTES Don’t Care Multiple bytes may be selected during the same cycle. ...

Page 8

... Output Timing Reference Levels 3729 drw 05 AC Test Load 8 Commercial and Industrial Temperature Ranges Min. Max. ___ 5 ___ 30 ___ Max ___ 0.4 2.4 ___ if not actively driven. SS IDT71V433S11 IDT71V433S12 Com'l. Ind. Com'l. Ind. 220 220 210 210 +3.3V 317 5pF* 351 3729 drw 04 * Including scope and jig capacitance ...

Page 9

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Symbol Clock Parameters t Clock Cycle Time CYC (1) t Clock High Pulse Width CH (1) t Clock Low Pulse Width CL Output Parameters t Clock High to Valid Data CD t Clock High to Data Change CDC (2) t Clock High to Output Active ...

Page 10

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Commercial and Industrial Temperature Ranges . 10 ...

Page 11

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Commercial and Industrial Temperature Ranges 11 6.42 . ...

Page 12

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Commercial and Industrial Temperature Ranges ...

Page 13

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Commercial and Industrial Temperature Ranges 13 6.42 . ...

Page 14

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Commercial and Industrial Temperature Ranges 14 . ...

Page 15

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs CLK ADSP ADSC ADDRESS Av GW, BWE, BWx CE DATA OUT NOTES input is LOW, ADV is HIGH, and LBO is Don’t Care for this cycle. 2. (Ax) represents the data for address Ax, etc. 3. For read cycles, ADSP and ADSC function identically and are therefore interchangeable. ...

Page 16

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs CLK ADSP ADSC ADDRESS DATA IN NOTES input is LOW, ADV and OE are HIGH, and LBO is Don't Care for this cycle. 2. (Ax) represents the data for address Ax, etc. 3. Although only GW writes are shown, the functionality of BWE and BWx together is the same as GW. ...

Page 17

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Commercial and Industrial Temperature Ranges 17 6.42 ...

Page 18

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs S X IDT 71V433 Device Power Speed Type PART NUMBER SPEED IN MEGAHERTZ 71V433S11PF 71V433S12PF PF X Package Process/ Temperature Range Blank PARAMETER CD 50 MHz MHz Commercial and Industrial Temperature Ranges Commercial ( +70 C) Industrial (– +85 C) ...

Page 19

... IDT71V433 32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs 09/10/99 Pg Pg. 3–5 Pg Pg. 11–14 Pg. 18 10/08/99 Pg 04/04/00 Pg. 17 08/09/00 08/17/01 CORPORATE HEADQUARTERS 2975 Stender Way Santa Clara, CA 95054 The IDT logo is a registered trademark of Integrated Device Technology, Inc. Updated to new format ...