CXD3500R Sony, CXD3500R Datasheet

CXD3500R

Specifications of CXD3500R

Available stocks

Related parts for CXD3500R

CXD3500R Summary of contents

Page 1

... Timing Generator for LCD Panels Description The CXD3500R is a timing signal generator for driving the LCD panels of Sony data projectors. This chip has a built-in serial interface circuit which supports various SXGA (skip scan display), XGA, SVGA and VGA signals, and (double speed) NTSC and PAL signals through external control from a microcomputer, etc ...

Page 2

... RGTCNT 10 FRPCNT 11 SCTR 60 SCLK 61 SERIAL DATA I/F SDAT SYNC DETECTOR AUX. PLL COUNTER & DECODER MASTER CLOCK PULSE ELIMINATOR V-POSITION COUNTER & DECODER V-TIMING PULSE GENERATOR TEST – 2 – CXD3500R 1 HSYNC 2 VSYNC XVS 50 51 XHS 53 ORACT FLD 6 VCK 33 VST 34 FRP 43 XFRP ...

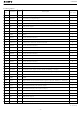

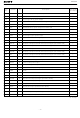

Page 3

... O BLK pulse output pulse output 32 ENB1 O ENB1 pulse output 33 VCK O Vertical display clock pulse output Description /2, min. Vp-p = 0.5V) DD – 3 – CXD3500R Input pin for open status — — — H — — — — — — H — — — — — ...

Page 4

... Serial clock input (serial transfer block) 62 SDAT I Serial data input (serial transfer block) 63 HDN O Phase comparator pulse output 64 CKI1 I Clock 1 input (TTL) Description – 4 – CXD3500R Input pin for open status — — — — — — — — — — — — ...

Page 5

... Typ. Max. Unit 5 0.3V DD Vp-p Ω 0.3V DD 0.8 V 0.4 – 0.8 V 0.4 – 0.8 V 0.4 – 0.8 V 0.4 10 –100 –240 µ µ CXD3500R Applicable pins CKI1 CKI2 1 HSYNC, VSYNC, SCTR, SCLK, SDAT FLD SHP1A, SHP2A At a 30pF load ...

Page 6

... HCK1 HCK2 5.0 ± 0.5V Item (V = 5.0 ± 0.5V Item – 6 – CXD3500R = 0V, Topr = –20 to +75°C) SS Min. Typ. Max. Conditions 18.2 18 30pF – 0V, Topr = –20 to +75°C) SS Min. Typ. Max. 4Tns 2Tns 4Tns 2Tns 2Tns 2Tns 5Tns 5Tns T: Input clock cycle = 0V, Topr = – ...

Page 7

... Note) See "Serial transfer timing" on page 11 for the timing relationship between D15 to D0 and each pulse. External clock input AC characteristics HSYNC (negative polarity) CKI1 10% 50% 50 50% 50 tw1H tw2 th1 ts1 th1 D14 D9 D8 th0 ts0 50% twL twH 50% 50% – 7 – 50 50 th0 tw3 50% 50 th0 ts0 50% 50% 50% CXD3500R D15 ...

Page 8

... A sync-separated, normal-speed VSYNC should be input as the vertical sync signal. b) The input sync signal polarity is not fixed, and is set by the serial data (VPOL). c) The phase relationship between HSYNC and VSYNC is specified as follows for the CXD3500R. (1) XGA, Macintosh16, SVGA, VGA, PC-98 HSYNC ...

Page 9

... PAL Sync signal phase reference VSYNC ODD FIELD HSYNC EVEN FIELD Notes) (2) and (3) show the timing when supporting input of double-speed signals. (4) and (5) show the timing when using the built-in double-speed controller (CXD3500R) and a line memory (µPD485505: NEC) H/2 – 9 – CXD3500R ...

Page 10

... The number of lines is counted by an internal counter and the vertical direction pulses (VST, FRP) are output at a specified cycle. For the CXD3500R, no signal (free running) status is judged if there is no VSYNC input for longer than the following periods (free running detection timing). ...

Page 11

... XCLR pin The CXD3500R should be forcibly reset during power on in order to initialize the serial transfer block and other internal circuits. At this time, the serial interface circuit is reset to the initial status (preset status). See page 38 for the preset settings. Serial transfer operation 1 ...

Page 12

... Control data When using the CXD3500R, set the control data corresponding to each LCD panel and video signal according to the formats in the table below. Address D15 D14 D13 D12 D11 D10 Note) PLLP0, HP0, VP0, HSTW0, HSTP0, PCGU0, PCGD0, PRGD0, FRPP0, SHP0, MBKA0, MBKB0, MBKZ0, IRD0, IRU0, ORRS0, ORP0, ORD0, ORU0, HAXD0, HAXU0, VAXD0, VAXU0: LSB ...

Page 13

... Setting data PAL double speed (762 572) PLLP setting value = 1880 (horizontal period) – 2 PLLP Setting data 1150 (LHLLLHHHHHHL: LSB 1054 (LHLLLLLHHHHL: LSB 798 (LLHHLLLHHHHL: LSB 846 (LLHHLHLLHHHL: LSB 1558 (LHHLLLLHLHHL: LSB 1878 (LHHHLHLHLHHL: LSB – 13 – CXD3500R VESA SVGA60 VGA60 ...

Page 14

... Reference: HDN transition point Thp Image display period Thp: Timing from the front edge of HSYNC to the HST pulse HSTP5 to 0: LLLLL, HDNPOL: H PLSSL2 Thp clk clk 118 clk 146 clk 178 clk 188 clk 204 clk 232 clk HSTP5 All L – 14 – CXD3500R HDNPOL: H ...

Page 15

... Minimum and maximum Tvp setting values Min Max Note) The time from VST until image display starts differs for each panel. Also see the data sheets of the used panels. Minimum adjustment width Tvp Tvp Minimum adjustment width Tvp 259H – 15 – CXD3500R ...

Page 16

... HP11 to 0 setting is large and the ENB pulses fall near the end of the horizontal period, the vertical display start position is offset by 1H. VSYNC HSYNC ENB1, 2 ENB1, 2 The counter is reset at this timing. The counter is reset at this timing. – 16 – CXD3500R When the HP11 to 0 setting is large. ...

Page 17

... CXD3500R clk 82 clk 90 clk 102 clk 116 clk 128 clk 144 clk 156 clk 176 clk ...

Page 18

... Note) HCK2 is the reverse polarity of HCK1. The timings shown above are for RGT: H, HCKPOL: H and HCKFX: L. Reference 3 clk Reference 11 clk Reference 6 clk Reference to LLHHHH (LSB) – 18 – CXD3500R HSTP5 to 0: LLLLHH (LSB) HSTP5 to 0: LLHLHH (LSB) to LLHHHH (LSB) HSTP5 to 0: LLLHHL (LSB) Same hereafter using this point as the reference. HSTP5 to 0: LHLLLL (LSB) ...

Page 19

... CXD3500R PCG: H Tpcd clk 104 clk 128 clk 154 clk 182 clk 212 clk 226 clk 252 clk ...

Page 20

... CXD3500R clk 112 clk 138 clk 166 clk 198 clk 212 clk 226 clk 252 clk ...

Page 21

... The PRG pulse rise position is the same as the FRP pulse transition point, and is interlinked with FRPP3 to 0. ENB1, 2 FRP PCG See SLCNT. 1F Tfrp Tfrp setting range FRPP3 PLSSL2 clk clk clk clk clk clk clk clk – 21 – CXD3500R clk 54 clk 66 clk 82 clk 98 clk 88 clk 92 clk 102 clk ...

Page 22

... XGA panel 12-dot simultaneous sampling VSTPOL DWN H — — RGT HCKPOL H — — HST HCK1 HCK2 HSTW1, 0: LL, HSTP5 to 0: LLLLHH, HCKM: L HCKM: L HCKM: H – 22 – CXD3500R VST pulse polarity —: don't care HCK polarity —: don't care B in the table above ...

Page 23

... This IC does not have a sample-and-hold pulse output, but instead allows control of the sample-and-hold position of the CXA2112R sample-and-hold driver and control of master clock inversion by setting the CXD3500R serial data and connecting the control pins. INV set by serial data is output as is from the INV (Pin 49). Connect this INV to INV_CNT (Pin 52) of the CXA2112R to allow CXA2112R dot clock phase inversion control from the TG ...

Page 24

... CXD3500R HDNPOL: H HDNPOL: L Tclp CLPP: L CLPP clk 32 clk 60 clk 40 clk 77 clk 53 clk 100 clk 68 clk 124 clk 84 clk 124 clk ...

Page 25

... Address: 07 Data 4 SLFLD This bit selects FLD (Pin 6) IN/OUT pin input and output. The CXD3500R performs field identification internally. When SLFLD is L, the internally generated FLD pulse is selected and used for the internal circuit logic. The external FLD pulse is selected by setting SLFLD to H. ...

Page 26

... BLKON: L, BLKPOL: H BLK BLKON: H, BLKPOL: L BLK BLKON: L, BLKPOL: L BLK LCD panel Setting reference L Dot clock 30MHz H Dot clock 40MHz SVGA L Dot clock 50MHz H Dot clock 63MHz L Dot clock 75MHz H Dot clock 80MHz XGA L Dot clock 85MHz H Dot clock 96MHz – 26 – CXD3500R ...

Page 27

... When MBKA4 LLLLL or LLLLH, skip scan is not performed. MBKB3 These bits set the sub skip scan position. The setting range is from 2 to 15. See the figures on the next page. When MBKB3 LLLL or LLLH, or when MBKB > MBKA, sub skip scan is not performed. FMBK: L (SUB) – 27 – CXD3500R ...

Page 28

... MBKA4 to 0: LHLLH, MBKB3 to 0: LLLL X VCK FRP To set 2/18 skip scan and odd line skip scan VCK FRP Sub skip scan position specified by MBKB Cycle set by MBKA Same polarity skip scan continues. MBKA4 to 0: HLLHL, MBKB3 to 0: HLLH – 28 – CXD3500R ...

Page 29

... FLD VST VCK FRP ENB HST/PCG FLD Note) Observe the following points when setting MBKZ3 When MBKB set the MBKZ value to MBKA or less all other cases, set the MBKZ value to MBKB or less MBKA: 10, MBKB: 5, FLD MBKA: 10, MBKB: 5, FLD: H – 29 – CXD3500R ...

Page 30

... The serial setting DWN is reflected to the DWN (Pin 37). In addition, RGT is valid only when SLCNT this time the setting value is reflected to the RGT (Pin 25). See page 22 of this data sheet for the relationship between the DWN and VST pulses and the RGT and HCK pulses. Reset the internal PLL counter at these timings. – 30 – CXD3500R ...

Page 31

... PLLP11 the correct value when using this mode, regardless of the serial data HR setting. ADC HSYNC VSYNC HSYNC RSTW WCK RSTR RCK HSYNC RSTW RSTR LINE Mem. PD485505 RSTW WCK CXD3500R MCK: f Double-speed display system diagram Double-speed display timing – 31 – DAC RSTR RCK f/2 f CXD3500R ...

Page 32

... XGBK to H. The output pulse timing is shown in the figure below. When not using black frame display, set XGBK to L. When using SVGA panels, BLKON: H, BLKPOL: H, SPON: L BLK PCG PRG When using XGA panels, BLKON: H, BLKPOL: L, SPON: H, XGBK: H BLK PCG PRG – 32 – CXD3500R ...

Page 33

... The reference position is the front edge of the ENB1 and 2 pulse that is 1H from the front edge of VSYNC. Labeling this position as 0, the pulse can be set to an arbitrary position. VSYNC ENB XVS Reference Arbitrary pulse output possible within the range of 700 clk 192 clk VAXON: H, VAXD11 to 0: LLLLLLLLLHHH, VAXU11 to 0: LLLLLLLLLLLL – 33 – CXD3500R SPON: H, HDON: H ...

Page 34

... Reset is not applied at the H cycle when ORRS4 to 0 (LSB) is LLLLL, and applied at the set number of cycles for other settings. Reset can be applied from maximum of 31H cycles. V-SYNC IRACT ORACT 4H Timing at which reset is applied to OR counter SLLAP: H, ORRS4 to 0: LLHLL, VRSP3 to 0: LLLH – 34 – CXD3500R ...

Page 35

... V-SYNC IRACT ORACT V-SYNC IRACT ORACT 128 clk IRD11 to 0: LLLLLLLLLLLL, IRU11 to 0: LLLLHLLLLLLL, HR: H 128 clk IRD11 to 0: LLLLLLLLLLLH, IRU11 to 0: LLLLHLLLLLLL, HR: H SLLAP: H, VRSP3 to 0: LLLH SLLAP: H, VRSP3 to 0: LHLH Timing at which reset is applied to OR counter – 35 – CXD3500R ...

Page 36

... HSYNC according to the serial data ORU11 to 0 and ORD11 to 0 settings. The IRACT and ORACT pulses can be set independently. SLLAP: H (asynchronous to HSYNC) HSYNC IRACT ORACT SLLAP: L (synchronous to HSYNC) HSYNC IRACT ORACT IRD11 to 0: LLLLLLLLLLLL, IRU11 to 0: LLLLHLLLLLLL ORD11 to 0: LLLLLLLLLLLL, ORU11 to 0: LLLLHLLLLLLL – 36 – CXD3500R ...

Page 37

... These bits are the setting data for the programmable pulses. When the above settings are made, the XVS (Pin 50) output switches to programmable pulse output, and this setting data is reflected. The XVS pulse is synchronized to the internal vertical counter, and can be output at an arbitrary position within one vertical period. (See page 33.) – 37 – CXD3500R ...

Page 38

... Set XCLR to H level and then make all the necessary settings. The preset setting values are shown in the table below. Address D15 D14 D13 D12 D11 D10 — — — — — — – 38 – Data — — — — —: Setting invalid CXD3500R — L — — — ...

Page 39

... XVS pulses are output with the VSYNC pulse that is latched by the XHS pulse when serial data VAXON addition, like XHS, programmable pulses are output when serial data VAXON is H. VSYNC HSYNC XHS XVS 128 clk 96 clk ORD11 to 0: LLLLLLLLLLLL, ORU11 to 0: LLLLHLLLLLLL XHS XVS – 39 – CXD3500R 2 clk ...

Page 40

... CXD3500R ...

Page 41

... CXD3500R ...

Page 42

... CXD3500R ...

Page 43

... CXD3500R ...

Page 44

... CXD3500R ...

Page 45

... CXD3500R ...

Page 46

... CXD3500R ...

Page 47

... CXD3500R ...

Page 48

... CXD3500R ...

Page 49

... CXD3500R ...

Page 50

... CXD3500R ...

Page 51

... CXD3500R ...

Page 52

... CXD3500R ...

Page 53

... CXD3500R ...

Page 54

... CXD3500R ...

Page 55

... CXD3500R ...

Page 56

... CXD3500R ...

Page 57

... CXD3500R ...

Page 58

... CXD3500R ...

Page 59

... CXD3500R ...

Page 60

... CXD3500R ...

Page 61

... CXD3500R ...

Page 62

... CXD3500R ...

Page 63

... CXD3500R ...

Page 64

... CXD3500R ...

Page 65

... CXD3500R ...

Page 66

... CXD3500R ...

Page 67

... CXD3500R ...

Page 68

... CXD3500R ...

Page 69

... CXD3500R ...

Page 70

... CXD3500R ...

Page 71

... CXD3500R ...

Page 72

... PLL IC: Sony CXA3106(A)Q (built-in phase comparator, frequency divider recommended. CLKH When not using skip scan, ENB1 and 2 are interchangeable. CXD2112R – 72 – S/H driver IC CXA2112R ENB1 BLK 29 HCK2 28 HCK1 HST 27 XRGT 26 RGT MODE1 22 MODE2 21 MODE3 20 XCLR 19 TEST7 18 CKI3 17 0.1 CXD3500R LCD panel 10k 1 /16V +5V 47 /16V ...

Page 73

... NOTE: Dimension “ ” does not include mold protrusion. DETAIL A PACKAGE STRUCTURE PACKAGE MATERIAL LEAD TREATMENT LQFP-64P-L01 LQFP064-P-1010 LEAD MATERIAL PACKAGE MASS – 73 – 0.05 0.127 – 0.02 + 0.2 0.1 EPOXY RESIN SOLDER/PALLADIUM PLATING 42/COPPER ALLOY 0.3g CXD3500R ...