CXD2510Q Sony, CXD2510Q Datasheet

CXD2510Q

Specifications of CXD2510Q

Available stocks

Related parts for CXD2510Q

CXD2510Q Summary of contents

Page 1

... CD Digital Signal Processor Description The CXD2510Q is a digital signal processor LSI for CD players and is equipped with the following functions. • Wide frame jitter margin (±28 frames) due to a built- in 32K RAM • Bit clock, which strobes the EFM signal, is generated by the digital PLL • ...

Page 2

... CLKO 80 MIRR EFM demodulator Address generator 8 data processor Error corrector CLV processor Timing generator – 2 – CXD2510Q 32K RAM Priority encoder 30 PSSL D/A DA01 MUTE Peak detector Digital out 60 DOUT MD2 59 71 DATA CPU interface 74 CLOK 72 XLAT 77 DATO Servo auto 79 CLKO ...

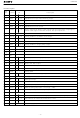

Page 3

... Low: asymmetry circuit off; high: asymmetry circuit on Audio data output mode switching input. Low: serial output; high: parallel output. D/A interface for 48-bit slot. Word clock f = 2Fs. D/A interface for 48-bit slot. LR clock f = Fs. Power supply (5V). – 3 – Description = 8.6436MHz. LOCK ). DD CXD2510Q ...

Page 4

... XUGF output when PSSL = 0. XPLCK output when PSSL = 0. GFS output when PSSL = 0. RFCK output when PSSL = 0. C2PO output when PSSL = 0. XRAOF output when PSSL = 0. MNT3 output when PSSL = 0. MNT2 output when PSSL = 0. MNT1 output when PSSL = 0. MNT0 output when PSSL = 0. – 4 – CXD2510Q ...

Page 5

... Serial data transfer clock input from CPU. SENS input from SSP. Track jump count signal input. Serial data output to SSP. Serial data latch output to SSP. Latched at the falling edge. Serial data transfer clock output to SSP. Mirror signal input. – 5 – Description CXD2510Q ...

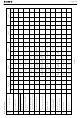

Page 6

... Conditions Min. V ( (2) 0. Schmitt input V ( (3) Analog input Vss –1mA V (1) V – 0 1mA V ( –1mA V (2) V – 0 2mA V ( 2mA V ( –0.28mA V (4) V – 0 0.36mA V ( 5.50V I – 5.50V – – 6 – CXD2510Q Applicable Typ. Max. Unit pins µ µA 8 ...

Page 7

... DD DD Min. Typ. Max. Unit 7 34 MHz = AV = 5.0V ± 10 Min. Typ. Max. Unit ns 13 500 13 500 ns 26 1,000 ns V – 1 WLX 5.0V ± 10 Min. Typ. Max. Unit 2.0 V +0.3 Vp-p DD – 7 – CXD2510Q V IHX V 0.9 IHX 0.1 IHX V ILX ...

Page 8

... The internal registers are initialized by a reset when XRST = 0; the initialization data is shown in Table 1- 0V, Topr = –20 to +75° Min. Typ. Max. 0.65 750 300 300 300 750 0.65 750 65 7 Data – 8 – Unit MHz MHz ns kHz µ 750ns or more Address Valid 300ns max CXD2510Q ...

Page 9

... CXD2510Q ...

Page 10

... CXD2510Q ...

Page 11

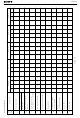

... Data 3 Timer range MT1 MT0 LSSL 0 AS1 RXF = 0 Forward RXF = 1 Reverse Timer range TR1 0.045ms 0.09ms KF1 KF0 SD1 SD0 5.8ms 2.9ms 2.9ms 1.45ms KF1 KF0 0.18ms 0.09ms CXD2510Q 0 0 AS0 0 RXF 1 RXF RXF RXF TR0 0.022ms 0.045ms ...

Page 12

... DA output mute is not affected when Digital out is either on or off. Data 1 Data Data D.out WSEL VCO SEL ASHS Mute-F Processing CDROM mode; average value interpolation and pre-value hold are not performed. Audio mode; average value interpolation and pre-value hold are performed. Processing Processing – 12 – Data 3 Data Data SOCT 0 CXD2510Q ...

Page 13

... Used for quadruple-speed and double-speed (quadruple correction) playback. Function Used for normal-speed and double-speed (double correction) playback. Used for quadruple-speed and double-speed (quadruple correction) playback. Function – 13 – DA output 0dB off –∞dB 0dB 0dB –∞dB 0dB –∞dB Application Use Use CXD2510Q ...

Page 14

... MDS = PWM polarity signal, carrier frequency of When DCLV PWM and MDP = PWM absolute value output (binary), MDS = Z When DCLV MDP = ternary PWM output, carrier frequency PWM and Processing – 14 – Data BiliGL 0 FLFC SUB Contents = 0, and 460Hz 132kHz. carrier frequency of 132kHz. of 132kHz and fc = 140Hz when CXD2510Q ...

Page 15

... The left and right channel inputs are output to the left and right channels for STEREO. ASEQ = 0 ASEQ = 1 Z SEIN (FZC) Z SEIN (A.S) Z SEIN (T.Z.C) Z SEIN (SSTOP) Z XBUSY Z FOK Z SEIN (Z) GFS GFS COMP COMP COUT COUT OV64 OV64 Z 0 Meaning Meaning BiliGL MAIN = 1 MAIN Mute – 15 – CXD2510Q ...

Page 16

... The maximum value for this status is then measured until the next readout. Data Mute ATT PCT1 Command bit PCM Gain ECC correction ability 0dB C1: double; C2: quadruple 0dB C1: double; C2: quadruple Mute C1: double; C2: double 0dB C1: double; C2: double – 16 – Data PCT2 0 0 –0.1% –0.2% XTal 0% Meaning ATT = 0 Attenuation off. ATT = 1 –12dB CXD2510Q ...

Page 17

... MDS0 Gain CLVS GCLVS Note) When DCLV = 0, the CLVS gain is as follows. When Gain CLVS = 0, GCLVS = –12dB. –12dB When Gain CLVS = 1, GCLVS = 0dB. –6dB –6dB 0dB 0dB +6dB – 17 – Data 3 Data Explanation Valid only when DCLV = 1. Valid when DCLV = CXD2510Q ...

Page 18

... Peak hold in CLVS mode at a cycle of RFCK/ Peak hold in CLVS mode at a cycle of RFCK/2. Note) Peak hold is performed at 34kHz in CLVH mode. Gain MDS1 Gain TB TP CLVS Explanation (See the Timing Chart 1-6.) Explanation – 18 – Gain GMDS MDS0 0 –6dB 1 0dB 0 +6dB See the $CX commands CXD2510Q ...

Page 19

... Automatic CLVS/CLVP switching mode. This mode is normally used during playback CM2 CM1 CM0 CM0 Mode 0 STOP See the Timing Chart 1-7. 0 KICK See the Timing Chart 1-8. 0 BRAKE See the Timing Chart 1-9. 0 CLVS 0 CLVH 1 CLVP 0 CLVA – 19 – Explanation CXD2510Q ...

Page 20

... CXD2510Q ...

Page 21

... CXD2510Q ...

Page 22

... CXD2510Q ...

Page 23

... Timing Chart 1-7 DCLV = 0 MDS MDP FSW MON DCLV = 1 DCLV PWM MDS MDP FSW and MON are the same as for DCLV = · 236 (ns Acceleration n · 236 (ns) n Output Waveforms with DCLV = 1 STOP STOP Z Z – 23 – CXD2510Q Z Deceleration Deceleration ...

Page 24

... MDS MDP FSW MON DCLV = 1 DCLV PWM MDS MDP H FSW and MON are the same as for DCLV = 0 DCLV = 1 DCLV PWM MDS MDP H FSW and MON are the same as for DCLV = 0 STOP L KICK KICK Z Z KICK H L – 24 – 7.6µs CXD2510Q ...

Page 25

... Timing Chart 1-9 DCLV = 0 MDS MDP FSW MON DCLV = 1 DCLV PWM MDS MDP L FSW and MON are the same as for DCLV = 0 DCLV =1 DCLV PWM MDS MDP H FSW and MON are the same as for DCLV = 0 BRAKE BRAKE – 25 – CXD2510Q ...

Page 26

... When SQSO goes high after SCOR is output, the CPU determines that new data (which passed the CRC check) has been loaded. • In the CXD2510Q, when 80-bit data is loaded, the order of the MSB and LSB is inverted for each byte result, although the sequence of bytes is the same, the bits within the bytes are now ordered LSB first. ...

Page 27

... Timing Chart 2-1 Internal PLL clock 4.3218 ±DMHz WFCK SCOR EXCK SBSO WFCK SCOR EXCK SBSO S0• S0•S1 Same 750ns max S0 · Same Subcode P.Q.R.S.T.U.V.W Read Timing – 27 – CXD2510Q ...

Page 28

... CXD2510Q ...

Page 29

... CXD2510Q ...

Page 30

... CXD2510Q ...

Page 31

... In an actual player, PLL is necessary to regenerate the channel clock because the fluctuation in the spindle rotation alters the width of the EFM signal pulses. The block diagram of this PLL is shown in Fig. 3-1. The CXD2510Q has a built-in three-stage PLL. • The first-stage PLL regenerates the variable pitch. LPF and VCO are necessary as external parts. ...

Page 32

... OSC 16.9344MHz X'Tal (384Fs) XTSL 2/1 MUX Digital PLL 1/4 1/1000 1/4 1/1000 + n Up down counter Vari-Pitch n = –217 to 168 Microcomputer control I/M I/N RFPLL CXD2510Q – 32 – LPF VPCO 19.78 to 13.26MHz VCKI Vari-Pitch PCO FILI FILO CLTV VCO V DD CXD2510Q VCO ...

Page 33

... For C2 correction, the code is created with 24-byte information and 4-byte parity. Both C1 and C2 are Reed Solomon codes with a minimum distance of 5. • The CXD2510Q uses refined super strategy to achieve double correction for C1 and quadruple correction for C2. • In addition, to prevent C2 miscorrection pointer is attached to data after C1 correction according to the C1 error status, the playback status of the EFM signal, and the operating status of the player. • ...

Page 34

... MNT2 MNT1 MNT0 §3-4. DA Interface • The CXD2510Q has two modes as DA interfaces. a) 48-bit slot interface This interface includes 48 cycles of the bit clock within one LRCK cycle, and is MSB first. When LRCK is high, the data is for the left channel. b) 64-bit slot interface This interface includes 64 cycles of the bit clock within one LRCK cycle, and is LSB first ...

Page 35

... CXD2510Q ...

Page 36

... CXD2510Q ...

Page 37

... There are three digital out formats: the type 1 format for broadcasting stations, the type 2 form 1 format for home use, and the type 2 form 2 format for the manufacture of software. The CXD2510Q supports type 2 form 1. In addition, regarding the clock accuracy of the channel status, level III is set automatically when the crystal clock is used and level II is variable pitch ...

Page 38

... FZC after FZC has been continuously high for a longer time than E. Connection diagram for using the auto sequencer (example) RF MIRR FOK C. out SENS SSP DATA CLK XLT MIRR FOK DATA CLOK CXD2510Q XLAT CNIN SENS SEIN DATO CLKO XLTO Fig. 3-7. – 38 – CXD2510Q Micro-computer ...

Page 39

... Command for SSP $03 Fig. 3-8. (b) Auto Focus Timing Chart Auto focus Focus search up FOK = H NO YES FZC = H Check whether FZC is NO continuously high for the period of time E set with register 5. YES FZC = L NO YES Focus servo ON END Blind E – 39 – CXD2510Q $08 ...

Page 40

... N- for the traverse monitor counter which is set in register B, and COMP will be monitored. When the falling edge of this COMP is detected, overflow G can be reset.) – 40 – CXD2510Q 16 16 ...

Page 41

... Fig. 3-9. (b) 1-Track Jump Timing Chart 1 Track Track kick sled servo WAIT (Blind A) CNIN = NO YES Track REV kick WAIT (Brake B) Track sled servo ON END Fig. 3-9. (a) 1-Track Jump Flow Chart $2C ($28) – 41 – (REV kick for REV jump) (FWD kick for REV jump) Brake B $25 CXD2510Q ...

Page 42

... Fig. 3-10. (b) 10-Track Jump Timing Chart 10 Track Track, sled FWD kick WAIT (Blind A) CNIN = 5 ? (Counts CNIN NO YES Track, REV kick C = Overflow ? NO Checks whether the CNIN cycle is longer than overflow C. YES Track, sled servo ON END CNIN 5count $2E ($2B) – 42 – CXD2510Q 5) Overflow C $25 ...

Page 43

... Track Track, sled FWD kick WAIT (Blind A) Counts CINI for the first 16 times CNIN (MIRR and MIRR for more times. NO YES Track REV kick C = Overflow NO YES Track servo ON WAIT (Kick D) Sled servo ON END Overflow $2E ($2B) $26 ($27) – 43 – CXD2510Q Kick D $25 ...

Page 44

... YES Track Servo ON Sled REV Kick END Fig. 3-12. (a) Fine Search Flow Chart Traverse Speed Control (Overflow G) & CNIN N count Fig. 3-12. (b) Fine Search Timing Chart – 44 – CXD2510Q Track jump is terminated by sending and latching $40 from the CPU. $40 (cancel) latch $27 ($26) $25 ...

Page 45

... Mode Select DCLVMD CLVS U/D: Up/down signal from the CLV-S servo. MDS error: Frequency error for CLV-P servo. MDP error: Phase error for CLV-P servo. Fig. 3-13. Block Diagram – 45 – CXD2510Q MDP Error Measure Over Sampling Filter-1 Gain MDP CLV P ...

Page 46

... Fig. 3-14. Example of an Asymmetry Compensation Application Circuit §3-9. Playback Speed In the CXD2510Q, the following playback modes can be selected through different combinations of the crystal, XTSL pin, double-speed command (DSPB), VCO selection command (VCOSEL) and command transfer rate selector (ASHS). Also, the minimum operating voltage changes according to the playback mode. ...

Page 47

... XLT RF1 CLK RF0 LOCK CC DV DIRC TZC SSTOP TDFCT ISET ATSC FSET FZC SL– FE SL0 FDFCT SL+ GND GND GND – 47 – CXD2510Q DEMP LRCK WDCK DATA BCLK MUTE C2PO V CC GND SS V XUGF GTOP (64) LRCK (64) BCLK (64) DATA (48) BCLK (48) DATA DD V (48) ...

Page 48

... QFP-80P-L051 LEAD TREATMENT LEAD MATERIAL QFP080-P-1420-AH PACKAGE WEIGHT – 48 – + 0.1 0.15 – 0.05 0. 0.2 0.1 – 0.05 + 0.35 2.75 – 0.15 EPOXY RESIN SOLDER PLATING COPPER / 42 ALLOY 1.6g A 1.45 0° to 10° DETAIL A EPOXY RESIN SOLDER PLATING 42 ALLOY 1.6g CXD2510Q ...