K4E641611D-TC50 Samsung, K4E641611D-TC50 Datasheet

K4E641611D-TC50

Specifications of K4E641611D-TC50

Related parts for K4E641611D-TC50

K4E641611D-TC50 Summary of contents

Page 1

... All of this family have CAS-before-RAS refresh, RAS-only refresh and Hidden refresh capabilities. This 4Mx16 EDO Mode DRAM family is fabricated using Samsung s advanced CMOS process to realize high band-width, low power consumption and high reliability. FEATURES • Part Identification - K4E661611D-TC(5.0V, 8K Ref.) - K4E641611D-TC(5.0V, 4K Ref.) • Active Power Dissipation Speed 8K -50 ...

Page 2

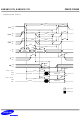

... K4E661611D, K4E641611D PIN CONFIGURATION (Top Views) • K4E661611D-T • K4E641611D DQ0 3 48 DQ1 4 47 DQ2 5 46 DQ3 DQ4 8 43 DQ5 9 42 DQ6 10 41 DQ7 RAS ...

Page 3

... K4E661611D, K4E641611D ABSOLUTE MAXIMUM RATINGS Parameter Voltage on any pin relative Voltage on V supply relative Storage Temperature Power Dissipation Short Circuit Output Current * Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability ...

Page 4

... K4E661611D, K4E641611D DC AND OPERATING CHARACTERISTICS Symbol Power I Don t care CC1 I Normal Don t care CC2 I Don t care CC3 I Don t care CC4 I Normal Don t care CC5 I Don t care CC6 Operating Current (RAS and UCAS, LCAS, Address cycling @ CC1 I : Standby Current (RAS=UCAS=LCAS=W=V CC2 RAS-only Refresh Current (UCAS=LCAS=V ...

Page 5

... K4E661611D, K4E641611D CAPACITANCE (T = Parameter Input capacitance [A0 ~ A12] Input capacitance [RAS, UCAS, LCAS, W, OE] Output capacitance [DQ0 - DQ15] AC CHARACTERISTICS ( Test condition : V =5.0V 10%, Vih/Vil=2.6/0.7V, Voh/Vol=2.0/0.8V CC Parameter Random read or write cycle time Read-modify-write cycle time Access time from RAS Access time from CAS ...

Page 6

... K4E661611D, K4E641611D AC CHARACTERISTICS (Continued) Parameter Data hold time Refresh period (4K, Normal) Refresh period (8K, Normal) Write command set-up time CAS to W delay time RAS to W delay time Column address W delay time CAS set-up time (CAS -before-RAS refresh) CAS hold time (CAS -before-RAS refresh) ...

Page 7

... K4E661611D, K4E641611D TEST MODE CYCLE Parameter Random read or write cycle time Read-modify-write cycle time Access time from RAS Access time from CAS Access time from column address RAS pulse width CAS pulse width RAS hold time CAS hold time Column Address to RAS lead time ...

Page 8

... K4E661611D, K4E641611D NOTES An initial pause of 200us is required after power-up followed by any 8 RAS-only refresh or CAS-before-RAS refresh cycles 1. before proper device operation is achieved. V (min) and V (max) are reference levels for measuring timing of input signals. Transition times are measured between (min) and V (max) and are assumed to be 2ns for all inputs ...

Page 9

... K4E661611D, K4E641611D t is specified from W falling edge to the earlier CAS rising edge. 16. CWL t 17. is referenced to the earlier CAS falling edge before RAS transition low. CSR 18 referenced to the later CAS rising edge after RAS transition low. CHR RAS LCAS UCAS t 19. ...

Page 10

... K4E661611D, K4E641611D WORD READ CYCLE RAS UCAS LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t CSH CRP t RCD t CSH CRP t RCD t RAD t t RAH ...

Page 11

... K4E661611D, K4E641611D LOWER BYTE READ CYCLE NOTE : D = OPEN RAS UCAS LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS CRP t CSH CRP t RCD t RAD t t RAH ...

Page 12

... K4E661611D, K4E641611D UPPER BYTE READ CYCLE NOTE : D = OPEN RAS CRP UCAS CRP LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t CSH t RCD t RAD t t RAH ...

Page 13

... K4E661611D, K4E641611D WORD WRITE CYCLE ( EARLY WRITE ) NOTE : D = OPEN OUT RAS UCAS LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t CSH CRP t RCD t CSH ...

Page 14

... K4E661611D, K4E641611D LOWER BYTE WRITE CYCLE ( EARLY WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t CSH ...

Page 15

... K4E661611D, K4E641611D UPPER BYTE WRITE CYCLE ( EARLY WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t CSH ...

Page 16

... K4E661611D, K4E641611D WORD WRITE CYCLE ( OE CONTROLLED WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t CSH t RCD ...

Page 17

... K4E661611D, K4E641611D LOWER BYTE WRITE CYCLE ( OE CONTROLLED WRITE ) NOTE : D = OPEN OUT RAS UCAS LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS CRP t CSH CRP ...

Page 18

... K4E661611D, K4E641611D UPPER BYTE WRITE CYCLE ( OE CONTROLLED WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t CSH ...

Page 19

... K4E661611D, K4E641611D WORD READ - MODIFY - WRITE CYCLE RAS CRP UCAS CRP LCAS ASR ROW A ADDR DQ0 ~ DQ7 I/OL DQ8 ~ DQ15 I/OL t RAS t t RCD RSH t t RCD RSH ...

Page 20

... K4E661611D, K4E641611D LOWER-BYTE READ - MODIFY - WRITE CYCLE RAS CRP UCAS CRP LCAS ASR ROW A ADDR DQ0 ~ DQ7 I/OL DQ8 ~ DQ15 RAS t t RCD RSH t RAD t CSH ...

Page 21

... K4E661611D, K4E641611D UPPER-BYTE READ - MODIFY - WRITE CYCLE RAS CRP UCAS CRP LCAS ASR ROW A ADDR DQ0 ~ DQ7 DQ8 ~ DQ15 I/OL t RAS t t RCD RSH t RAD t CSH ...

Page 22

... K4E661611D, K4E641611D HYPER PAGE MODE WORD READ CYCLE RAS CRP UCAS CRP LCAS ASR RAH ROW A ADDR DQ0 ~ DQ7 DQ8 ~ DQ15 RASP t CSH ...

Page 23

... K4E661611D, K4E641611D HYPER PAGE MODE LOWER BYTE READ CYCLE RAS CRP UCAS LCAS ASR RAH ROW A ADDR DQ0 ~ DQ7 DQ8 ~ DQ15 RASP t CSH ...

Page 24

... K4E661611D, K4E641611D HYPER PAGE MODE UPPER BYTE READ CYCLE RAS CRP UCAS CRP LCAS ASR ROW A ADDR DQ0 ~ DQ7 DQ8 ~ DQ15 RASP t CSH ...

Page 25

... K4E661611D, K4E641611D HYPER PAGE MODE WORD WRITE CYCLE ( EARLY WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR RAH ROW A ADDR DQ0 ~ DQ7 DQ8 ~ DQ15 ...

Page 26

... K4E661611D, K4E641611D HYPER PAGE MODE LOWER BYTE WRITE CYCLE ( EARLY WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR RAH ROW A ADDR DQ0 ~ DQ7 ...

Page 27

... K4E661611D, K4E641611D HYPER PAGE MODE UPPER BYTE WRITE CYCLE ( EARLY WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR RAH ROW A ADDR DQ0 ~ DQ7 ...

Page 28

... K4E661611D, K4E641611D HYPER PAGE MODE WORD READ - MODIFY - WRITE CYCLE RAS CRP UCAS CRP LCAS RAD t t ASR ASC ROW A ADDR DQ0 ~ DQ7 I/OL DQ8 ~ DQ15 CSH ...

Page 29

... K4E661611D, K4E641611D HYPER PAGE MODE LOWER BYTE READ - MODIFY - WRITE CYCLE RAS CRP UCAS CRP LCAS RAD t t ASR ASC ROW A ADDR DQ0 ~ DQ7 I/OL DQ8 ~ DQ15 ...

Page 30

... K4E661611D, K4E641611D HYPER PAGE MODE UPPER BYTE READ - MODIFY - WRITE CYCLE RAS CRP UCAS CRP LCAS RAD t t ASR ASC ROW A ADDR DQ0 ~ DQ7 I/OL DQ8 ~ DQ15 ...

Page 31

... K4E661611D, K4E641611D HYPER PAGE READ AND WRITE MIXED CYCLE RAS UCAS LCAS t RAD RAH t ASR ROW A ADDR DQ0 ~ DQ7 I/OL DQ8 ~ DQ15 I/OL t RASP t t READ( ) READ( ) CAC ...

Page 32

... K4E661611D, K4E641611D RAS - ONLY REFRESH CYCLE NOTE : Don t care OPEN OUT RAS CRP UCAS CRP LCAS ASR RAH ROW A ADDR CAS - BEFORE - RAS REFRESH CYCLE NOTE : OE Don t care ...

Page 33

... K4E661611D, K4E641611D HIDDEN REFRESH CYCLE ( READ ) RAS CRP UCAS CRP LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 Hidden refresh cycle of 64Mb A-die & B-die, when CAS signal transits from Low to High, the valid data may be cut off. ...

Page 34

... K4E661611D, K4E641611D HIDDEN REFRESH CYCLE ( WRITE ) NOTE : D = OPEN OUT RAS CRP UCAS CRP LCAS ASR ADDRESS DQ0 ~ DQ7 DQ8 ~ DQ15 RAS t t RCD ...

Page 35

... K4E661611D, K4E641611D CAS - BEFORE - RAS SELF REFRESH CYCLE NOTE : Don t care RAS UCAS LCAS DQ0 ~ DQ7 CEZ DQ8 ~ DQ15 TEST MODE IN CYCLE NOTE : Don t care RAS ...

Page 36

... K4E661611D, K4E641611D PACKAGE DIMENSION 50 TSOP(II) 400mil 0.034 (0.875) 0.841 (21.35) MAX 0.821 (20.85) 0.829 (21.05) 0.0315 (0.80) 0.002 (0.05) MIN 0.010 (0.25) 0.018 (0.45) CMOS DRAM Units : Inches (millimeters) 0.004 (0.10) 0.010 (0.25) 0.047 (1.20) 0.010 (0.25) MAX TYP 0.018 (0.45) 0.030 (0.75) O 0~8 ...