80C186-16 Advanced Micro Devices, 80C186-16 Datasheet

80C186-16

Related parts for 80C186-16

80C186-16 Summary of contents

Page 1

... CMOS High-Integration 16-Bit Microprocessors Amendment (specifica- tions for the 20-MHz industrial operating range). This amendment consists of two parts: n Clock generation information changes for the 80C186 and 80C188 microcontrollers. If the guidelines in this bulletin are not followed, you may experience problems with clock start-up. ...

Page 2

... Crystal Inverting Amplifier Configuration Fundamental 20 MHz Figure 1. Oscillator Configurations and Recommended Crystal Modes 2 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment Crystal 200 pF b. Crystal Configuration Notes: 1. Use for third overtone mode crystals. Fundamental mode crystals do not use L1 or the 200-pF capacitor ...

Page 3

... Queue Status Waveforms” on page 15 n “RESET and HOLD/HLDA Timings” on page 16 n “RESET Waveforms” on page 16 n “HOLD/HLDA Waveforms (Entering HOLD)” on page 17 n “HOLD/HLDA Waveforms (Leaving HOLD)” on page 17 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 4

... All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with C = 50–100 pF (10–20 MHz). For AC tests, input Equal loading. 3. DEN, INTA, WR. 4 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 5

... If latched, A1 and A2 are selected instead of PCS5 and PCS6; only t 3. For write cycle followed by read cycle next bus cycle Changes in t-state preceding next bus cycle if followed by write. 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 6

... All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with C = 50–100 pF (10–20 MHz). For AC tests, input Equal loading. 3. DEN, INTA, WR. 6 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 7

... If latched, A1 and A2 are selected instead of PCS5 and PCS6; only t 3. For write cycle followed by read cycle next bus cycle Changes in t-state preceding next bus cycle if followed by read, INTA, or halt. 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 8

... MHz) and C = 50–100 pF (12.5–20 MHz). For AC tests, input where – 0 Equal loading. 3. DEN, INTA, WR. 8 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment Preliminary 20 MHz Min ...

Page 9

... For write cycle followed by interrupt acknowledge cycle. 5. LOCK is active upon t of the first interrupt acknowledge cycle and inactive upon Changes in t-state preceding next bus cycle if followed by write. 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 10

... MHz) and C = 50–100 pF (12.5–20 MHz). For AC tests, input where – 0 Equal loading. 3. DEN, INTA, WR. 10 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment Preliminary 20 MHz Min Max Unit 3 29 ...

Page 11

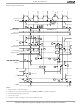

... CLKOUT 3 S2–S0 5 A19/S6–A16/S3, AD15–AD8/A15–A8, AD7–AD0 ALE 9 DEN DT/R 22 Notes: 1. For write cycle followed by halt cycle. 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment Status Invalid Address (Note ...

Page 12

... Low and High times) should not have a duration less than 40 CLCK CHCK 3. Tested under worst case conditions Not tested. 5. Tested under worst case conditions 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 0.45 V and V = 2.4 V, except at X1 where ...

Page 13

... Clock Waveforms X1 39 CLKOUT 41 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 14

... MHz). For AC tests, input guarantee proper operation guarantee recognition at clock edge. Synchronous Read (SRDY) Waveforms CLKOUT SRDY 14 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 0.45 V and V = 2.4 V, except at X1 where V IL ...

Page 15

... ARDY Normally Ready System) Peripheral and Queue Status Waveforms CLKOUT 53 INT3–INT0, NMI, TEST, TMR IN DRQ0, DRQ1 TMR OUT QS0, QS1 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 16

... MHz). For AC tests, input guarantee recognition at next clock. RESET Waveforms X1 57 RES CLKOUT RESET 16 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 0.45 V and V = 2.4 V, except at X1 where Preliminary ...

Page 17

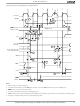

... DT/R, S2–S0, LOCK HOLD/HLDA Waveforms (Leaving HOLD) CLKOUT 58 HOLD HLDA AD15–AD8/A15–A8, AD7–AD0, DEN A19/S6–A16/S3, RD, WR, , DT/R, BHE/RFSH S2–S0, LOCK 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...

Page 18

... AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Am186, Am188, and E86 are trademarks of Advanced Micro Devices, Inc. Product names used in this publication are for identification purposes only and may be trademarks of their respective companies. 18 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment ...