MAX9404 Maxim, MAX9404 Datasheet

MAX9404

Related parts for MAX9404

MAX9404 Summary of contents

Page 1

... An enable input provides the ability to force all the outputs to a differential low state. The MAX9401 has high-impedance (open) input and the MAX9404 has an integrated 100Ω differential input termination, which reduces external component count. Both devices have double amplitude swing open emit- ter outputs suitable for driving long cables ...

Page 2

... ILD CC A CONDITIONS Figure 3 IHD Figure 3 ILD Figure 3 ID EN, EN, SEL, SEL, IN_, IN_, MAX9401 CLK, or CLK = EN SEL, SEL, CLK, or MAX9404 CLK = IHD MAX9404 Figure 3 OL Figure 3 OCM I (Note 4) EE MIN TYP MAX 2 ...

Page 3

... Propagation Delay IN to OUT Channel-to-Channel Skew CLK to OUT Channel-to- Channel Skew Maximum Clock Frequency f CLK(MAX) Maximum Data Frequency f Added Random Jitter (Note 7) Added Deterministic Jitter (Note CLK Setup Time CLK to IN Hold Time Output Rise Time Output Fall Time Propagation Delay Temperature ∆ ...

Page 4

Quad ECL/PECL Differential Buffers/Receivers (Outputs terminated with 50Ω 3.3V SEL = low, input transition time = 125ps (20% to 80%), f SUPPLY CURRENT vs. TEMPERATURE 100 OUTPUTS ARE OPEN; INPUTS ARE HIGH OR LOW 94 ...

Page 5

... Figure 1 shows the input and output configuration of the MAX9401/MAX9404. The MAX9401 has high- impedance inputs and requires external termination. The MAX9404 has integrated 100Ω differential input termination resistors across each of the four inputs (IN_ to IN_), reducing external component count. The MAX9401/MAX9404 have double-swing open-emit- ter outputs as shown in Figure 1 ...

Page 6

... In asynchronous mode, the CLK sig- IN_ 100Ω IN_ 1kΩ Figure 2. Input Bias Circuits for Unused Pins for MAX9401/MAX9404 6 _______________________________________________________________________________________ nal should be set to either logic low or high state to min- imize noise coupling. 100Ω ...

Page 7

... Use multiple bypass vias for connection to minimize inductance. Input and output trace characteristics affect the perfor- mance of the MAX9401/MAX9404. Connect each of the inputs and outputs to a 50Ω characteristic impedance trace. Avoid discontinuities in differential impedance and maximize common-mode noise immunity by main- ...

Page 8

Quad ECL/PECL Differential Buffers/Receivers CLK CLK IN_ IN_ OUT_ OUT_ Figure 5. CLK to OUT Propagation Delay Timing Diagram taining the distance between differential traces and avoid sharp corners. Minimize the number of vias to prevent impedance discontinuities. Reduce reflections ...

Page 9

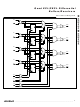

IN0 IN0 CLK CLK IN1 IN1 CLK CLK IN2 IN2 CLK CLK IN3 IN3 CLK CLK CLK CLK SEL SEL EN EN _______________________________________________________________________________________ Quad ...

Page 10

Quad ECL/PECL Differential Buffers/Receivers 10 ______________________________________________________________________________________ Package Information ...

Page 11

Quad ECL/PECL Differential ______________________________________________________________________________________ Buffers/Receivers Package Information (continued) 11 ...

Page 12

Quad ECL/PECL Differential Buffers/Receivers 12 ______________________________________________________________________________________ Package Information (continued) ...

Page 13

... Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________ 13 © ...