AT90LS2333 ATMEL Corporation, AT90LS2333 Datasheet

AT90LS2333

Related parts for AT90LS2333

AT90LS2333 Summary of contents

Page 1

... PDIP and 32-pin TQFP • Operating Voltage – 2.7V - 6.0V (AT90LS2333 and AT90LS4433) – 4.0V - 6.0V (AT90S2333 and AT90S4433) • Speed Grades – MHz (AT90LS2333 and AT90LS4433) – MHz (AT90S2333 and AT90S4433) Pin Configurations TQFP Top View (INT1) PD3 1 24 PC1 (ADC1) ...

Page 2

... The AT90S2333/4433 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits. Table 1. Comparison Table Device Flash AT90S2333 2K AT90LS2333 2K AT90S4433 4K AT90LS4433 4K AT90S/LS2333 and AT90S/LS4433 2 ...

Page 3

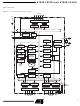

Block Diagram Figure 1. The AT90S2333/4433 Block Diagram VCC GND AVCC ANALOG MUX AGND AREF PROGRAM COUNTER PROGRAM FLASH INSTRUCTION REGISTER INSTRUCTION DECODER CONTROL LINES PROGRAMMING LOGIC DATA REGISTER PORTB AT90S/LS2333 and AT90S/LS4433 PC0 - PC5 PORTC DRIVERS DATA REGISTER ...

Page 4

Pin Descriptions VCC Supply voltage GND Ground Port B (PB5..PB0) Port 6-bit bi-directional I/O port with internal pullup resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled ...

Page 5

Architectural Overview The fast-access register file concept contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This means that during one single clock cycle, one Arithmetic Logic Unit (ALU) operation is executed. Two operands ...

Page 6

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, Timer/Counters, A/D- converters, and other I/O functions. The I/O Memory can be accessed directly the Data Space locations following those of the register file, ...

Page 7

Register Summary Address Name Bit 7 $3F ($5F) SREG I $3E ($5E) Reserved - $3D ($5D) SP SP7 $3C ($5C) Reserved $3B ($5B) GIMSK INT1 $3A ($5A) GIFR INTF1 $39 ($59) TIMSK TOIE1 $38 ($58) TIFR TOV1 $37 ($57) Reserved ...

Page 8

Register Summary (Continued) Address Name Bit 7 $02 ($22) Reserved $01 ($21) Reserved $00 ($20) Reserved Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written. ...

Page 9

Instruction Set Summary Mnemonics Operands Description ARITHMETIC AND LOGIC INSTRUCTIONS ADD Rd, Rr Add two Registers ADC Rd, Rr Add with Carry two Registers ADIW Rdl,K Add Immediate to Word SUB Rd, Rr Subtract two Registers SUBI Rd, K Subtract ...

Page 10

Instruction Set Summary (Continued) Mnemonics Operands Description DATA TRANSFER INSTRUCTIONS MOV Rd, Rr Move Between Registers LDI Rd, K Load Immediate LD Rd, X Load Indirect LD Rd, X+ Load Indirect and Post-Inc Load Indirect and ...

Page 11

... Wide, Plastic Dual in Line Package (PDIP) 32A 32-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP) AT90S/LS2333 and AT90S/LS4433 Ordering Code Package AT90LS2333-4AC 32A AT90LS2333-4PC 28P3 AT90LS2333-4AI 32A AT90LS2333-4PI 28P3 AT90S2333-8AC 32A AT90S2333-8PC 28P3 AT90S2333-8AI 32A AT90S2333-8PI 28P3 AT90LS4433-4AC 32A ...

Page 12

Packaging Information 28P3, 28-lead, 0.300” Wide, Plastic Dual Inline Package (PDIP) Dimensions in Inches and (Millimeters) AT90S/LS2333 and AT90S/LS4433 12 32A, 32-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP) Dimensions in Millimeters and (Inches) PIN 1 ID ...

Page 13

... Atmel Corporation 1999. Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard war- ranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein ...