pi6c2972 Pericom Semiconductor Corporation, pi6c2972 Datasheet

pi6c2972

Manufacturer Part Number

pi6c2972

Description

Low Voltage Pll Clock Driver Semiconductor Corporation

Manufacturer

Pericom Semiconductor Corporation

Datasheet

1.PI6C2972.pdf

(7 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

pi6c2972FC

Manufacturer:

PIC

Quantity:

1 831

1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2

1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 2 3 4 5 6 7 8 9 0 1 2

Features

• Fully Integrated PLL

• Output Frequency up to 125 MHz

• Compatible with PowerPC and Pentium Microprocessors

• 3.3V V

• + 100ps Typical Cycle–to–Cycle Jitter

• Packaging (Pb-free & Green available):

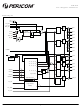

Pin Configuration

- 52-pin LQFP (FC)

VCO_Sel

GNDO

VCCO

VCCO

GND0

fselb1

fselb0

fsela1

fsela0

Qa3

Qa2

Qa1

Qa0

CC

40

41

42

43

44

45

46

47

48

49

50

51

52

39 38 37 36 35 34 33 32 31 30 29 28 27

1

2

3

4

5

6

7

8

9 10 11 12 13

26

25

24

23

22

21

20

19

18

17

16

15

14

fselFB1

QSync

GNDO

Qc0

VCCO

Qc1

fselc0

fselc1

Qc2

VCCO

Qc3

GND0

Inv_Clk

1

Description

The PI6C2972 are 3.3V compatible, PLL based clock driver devices

targeted for high-performance CISC or RISC processor based sys-

tems. With output frequencies of up to 125 MHz and skews of 550ps

the PI6C2972 are ideally suited for most synchronous systems. The

devices offer twelve low skew outputs plus a feedback and sync

output for added flexibility and ease of system implementation.

The PI6C2972 features an extensive level of frequency programma-

bility between the 12 outputs as well as the input vs output

relationships. Using the select lines output frequency ratios of 1:1,

2:1, 3:1, 3:2, 4:1, 4:3, 5:1, 5:2, 5:3, 6:1 and 6:5 between outputs can be

realized by pulsing low one clock edge prior to the coincident edges

of the Qa and Qc outputs. The Sync output will indicate when the

coincident rising edges of the above relationships will occur. The

Power–On Reset ensures proper programming if the frequency

select pins are set at power up. If the fselFB2 pin is held high, it may

be necessary to apply a reset after power–up to ensure synchroni-

zation between the QFB output and the other outputs. The internal

power–on reset is designed to provide this function, but with

power–up conditions being dependent, it is difficult to guarantee.

All other conditions of the fsel pins will automatically synchronize

during PLL lock acquisition.

The PI6C2972 offers a very flexible output enable/disable scheme.

Note that all of the control inputs on the PI6C2972 have internal pull–

up resistors.

The PI6C2972 is fully 3.3V compatible and requires no external loop

filter components. All inputs accept LVCMOS/LVTTL compatible

levels while the outputs provide LVCMOS levels with the capability

to drive 50-ohm transmission lines. For series terminated lines each

PI6C2972 output can drive two 50-ohm lines in parallel thus effec-

tively doubling the fanout of the device.

Low Voltage PLL Clock Driver

PI6C2972

PS8590C

09/22/04