sc1210str Semtech Corporation, sc1210str Datasheet - Page 7

sc1210str

Manufacturer Part Number

sc1210str

Description

Sc1210 High-speed 12 V Synchronous Power Mosfet Driver

Manufacturer

Semtech Corporation

Datasheet

1.SC1210STR.pdf

(9 pages)

THEOR

THEOR

UVLO

UVLO

Gat

Gat

VID-on-Fly Operation

VID-on-Fly Operation

THEOR

THEORY OF OPERA

THEOR

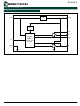

The SC1210 is a high speed, dual output driver designed

to drive top and bottom MOSFETs in a synchronous Buck

converter. It features adaptive delay for shoot-through

protection, VID-on-Fly operation, and internal LDO for op-

timum gate drive voltage. These drivers combined with

variety of Semtech PWM controllers form multi-phase

voltage regulators for advanced microprocessors.

UVLO

UVLO

UVLO

A supply voltage has to be applied to VIN pin of the

SC1210. The top and bottom gates are held low until

VIN exceeds UVLO threshold of the driver. Then the top

gate remains low and the bottom gate is pulled high to

turn on the bottom FET.

Gat

Gat

Gate T

Refer to the timing diagrams section, the rising edge of

the PWM input initiates the bottom FET turn-off and the

top FET turn-on. After a short propagation delay (t

the bottom gate begins to fall (t

in the SC1210 monitors the bottom gate voltage to drop

below 1.4V. Then after a preset delay time (t

expired, the top gate turns on. The delay time is set to

be 20ns typically. This prevents the top FET from turning

on until the bottom FET is off. During the transition, the

inductor current is freewheeling through the body diode

of either bottom FET or top FET, upon the direction of

the inductor current. The phase node could be low

(ground) or high (VIN).

The falling edge of the PWM input controls the top FET

turn-off and the bottom FET turn-on. After a short propa-

gation delay (t

As the inductor current is commutated from the top FET

to the body diode of the bottom FET, the phase node

begins to fall. The adaptive circuit in the SC1210 de-

tects the phase node voltage. It holds the bottom FET

off until the phase node voltage has dropped below 1.0V.

This prevents the top and bottom FETs from conducting

simultaneously or shoot-through.

VID-on-Fly Operation

VID-on-Fly Operation

VID-on-Fly Operation

Certain new processors have required to changing the

VID dynamically during the operation, or refered as VID-

on-Fly operation. A VID-on-Fly can occur under light load

Applications Information

POWER MANAGEMENT

2003 Semtech Corp.

e T

e T

e T

e Transition and Shoo

Y OF OPERA

Y OF OPERA

Y OF OPERATION

Y OF OPERA

ransition and Shoo

ransition and Shoo

ransition and Shoot Thr

ransition and Shoo

PDL_TG

), the top gate begins to fall (t

TION

TION

TION

TION

t Thr

t Thr

t Through Pr

t Thr

F_BG

ough Pr

ough Pro o o o o t t t t t ection

ough Pr

ough Pr

). An adaptive circuit

ection

ection

ection

ection

PDH_TG

PDL_BG

F_TG

) is

),

).

7

or heavy load conditions. At light load, it could force the

converter to sink current. Upon turn-off of the top FET,

the reversed inductor current has to be freewheeling

through the body diode of the top FET instead of the

bottom FET. As a result, the phase node voltage remains

high. The SC1210 incorporates the ability by pulling the

bottom gate to high internally, which over rides the adap-

tive circuit and turns the bottom FET on. The delay time

from the PWM falling egde to the bottom gate turn-on is

set at 200ns typically.

Optimized Gat

Optimized Gat

Optimized Gate Driv

Optimized Gat

Optimized Gat

With the supply voltage in between 9V to 16V, an inter-

nal LDO is designed with the SC1210 to bring the volt-

age to a lower level for gate drive. An external Ceramic

capacitor(1uF to 4.7uF) connected in between Vreg to

ground is needed to decouple the LDO. The LDO output

powers up the low gate driver, and the high gate drive is

powered by the external bootstrap circuit. The LDO out-

put voltage is set at 8.5V. The manufacture data and

bench tested results show that, for low R

at applied load current, the optimum gate drive voltage

is around 8.5V, where the total power losses of power

FETs, including conduction loss, switching loss, and the

gate drive loss, are minimized.

Thermal Shut Down

Thermal Shut Down

Thermal Shut Down

Thermal Shut Down

Thermal Shut Down

The SC1210 will shut down by pulling both driver out-

puts low if its junction temperature, T

COMPONENT SELECTION

COMPONENT SELECTION

COMPONENT SELECTION

COMPONENT SELECTION

COMPONENT SELECTION

Bootstrap Circuit

Bootstrap Circuit

Bootstrap Circuit

Bootstrap Circuit

Bootstrap Circuit

The SC1210 uses an external bootstrap circuit to pro-

vide a voltage for the top FET drive. This voltage, refer-

ring to the Phase Node, is held up by a bootstrap ca-

pacitor.

Typically, it is recommended to use a 1uF ceramic ca-

pacitor with 25V rating and a commonly available diode

IN4148 for the bootstrap circuit. In addition, a small

resistor may be added in between DRN of the SC1210

and the Phase Node. The resistor is used to allievate

the stress of the SC1210 from exposing to the negative

spike on the DRN pin. A negative spike could occur at

e Driv

e Drive V

e Driv

e Driv

e V

e V

e Voltage

e V

oltage

oltage

oltage

oltage

j

, exceeds 155°C.

www.semtech.com

SC1210

dson

FETs run