ingr165b ETC-unknow, ingr165b Datasheet

ingr165b

Available stocks

Related parts for ingr165b

ingr165b Summary of contents

Page 1

... Shielded-Twisted-Pair (STP) cables for distances meters and can directly interface to inputs of fiber optic modules to span longer distances. The INGR165B Receiver converts the serial bit-stream to the original parallel data format, fully transparent and without protocol overhead. Link-synchronization, bit-stream coding/decoding, clock-/frame- recovery and parity-check are managed by internal high-speed resources ...

Page 2

... It is required to use ceramic RF capacitors. With conventional 850 nm fiber optic modules (AC in/out, 3.3V PECL) and multimode fiber distances up to 550 meters have been achieved, see also datasheet of the ING_TRF fiberoptical piggyback board. 10/2003 - rev. 2.0 INGT165B / INGR165B ® link with STP copper cable is: ® ...

Page 3

... GigaSTaR INGT165B TRANSMITTER 2.1 BLOCK DIAGRAM RDCLK PDATA[35..0] Tx_SHIFTER PARITY VALID SHIFTER CTRL RESET# Figure 2: GigaSTaR 10/2003 - rev. 2.0 INGT165B / INGR165B OSC EXTRC1 LOCK 1.32 GHz CLOCK GENERATOR CLOCK FRAMER HEADER MUX CTRL (FLOW CONTROL & HEADER GENERATOR ) PERR# PARGEN FLAGI ® ...

Page 4

... PERR# is always inactive when PARGEN = '1'. The default value of PERR# after reset is ‘1’. 10/2003 - rev. 2.0 RESET# LOCK SYNGEN PARGEN GigaST#R £ INGT165B FLAGI TRANSMITTER VALID RDCLK PARITY PERR# ® Transmitter Parallel Interface ® INGT165B / INGR165B SDATA SDATA# link to maintain synchronization ...

Page 5

... Therefore both signals have least 50us at high state before transmitter is operational. Table 1: INGT165B Data Burst Timing Parameters (under recommended operating conditions) 10/2003 - rev. 2 2-1 2-2 DW1 DW2 PARITY1 PARITY2 INGT165B / INGR165B DW3 PARITY3 t 4 Min. Typ. Max. Unit ...

Page 6

... Note : For timings with assertion of FLAGI, please see section 3.2 dislock pulse generates an internal transmitter reset. Therefore both signals have least 50us at high state before transmitter is operational. Table 2: INGT165B Single Word Transfer Timing Parameters (Under recommended operating conditions) 10/2003 - rev. 2.0 INGT165B / INGR165B ...

Page 7

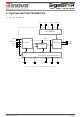

... GigaSTaR INGR165B RECEIVER 3.1 BLOCK DIAGRAM OSC LOCK CLOCK GENERATOR SDATA DE_SERIALIZER SDATA# FLAGO LSYNC# Figure 6: GigaSTaR 10/2003 - rev. 2.0 INGT165B / INGR165B EXTRC1 EXTRC2 1.32 GHz CLOCK DEFRAMER RES PERR# RESET# ® Receiver Block Diagram WRCLK RX_SHIFTER PDATA[35..0] PARITY ...

Page 8

... INGR165B RECEIVER PARALLEL INTERFACE SDATA SDATA# Figure 7: GigaSTaR 3.2.1 Control Signals RESET asynchronous active low reset signal. After a power-up sequence and activation of the reference clock, RESET# has to be kept low for at least 1 ms. The link is operational as soon as the LSYNC# signal is going low. ...

Page 9

... Figure 9: INGR165B Single Word Transfer Timing Diagram Parameter Description t Rising edge WRCLK to PDATA and PARITY valid 13 t WRCLK high state 14 Table 4: INGR165B Single Word Transfer Timing Parameters (under recommended operating conditions) 10/2003 - rev. 2.0 INGT165B / INGR165B DW1 DW2 PARITY1 PARITY2 Min ...

Page 10

... RESET# LOCK LSYNC# WRCLK PDATA [35..0] PARITY FLAGO Note : * indicates the data words [DW1, DW3] that are marked by the FLAGI signal. Figure 10: INGT165B / INGR165B FLAGI and FLAGO Timing Diagram Parameter Description t Rising edge of RDCLK to rising edge of FLAGI 15 t FLAGI minimum high state ...

Page 11

... Rising edge of WRCLK marking the corrupt data word to 21 rising edge of LSYNC# t Rising edge of WRCLK marking the corrupt data word to 22 falling edge of PERR# Table 6: INGR165B Parity Error (reporting) timing (under recommended operating conditions) 3.2.7 Header/Frame Error (Reporting) Timing LSYNC # WRCLK DW1 PDATA [35..0] PERR# ...

Page 12

... V 0 Vcc IN I -10 +10 OUTCML I -10 +10 OUTCMOS T -40 +125 j T -40 +85 a Min pF) L Table 10: AC – Characteristics INGT165B / INGR165B Units Note +4.2 V See handling precautions (6) +0 +20 mA See handling precautions (6) +140 C +150 sec V Human Body Model ± 800 V Human Body Model ...

Page 13

... Frequency Tolerance Duty Cycle External Loop Filter Specification 4.3.4 EXTRC1 The internal PLLs of the INGT165B and the INGR165B devices require an external RC loop filter not required to use dedicated RF R- and C-components, std components will perform correctly. Parameter Loop Filter Capacity Loop Filter Resistor 1 ...

Page 14

... Rising edge of WRCLK marking the corrupt data header to 23 rising edge of LSYNC# t Rising edge of WRCLK marking the corrupt data header to 24 falling edge of PERR# t PERR # low state 25 Table 14: Transmitter and Receiver Timing Parameters (under recommended operating conditions) 10/2003 - rev. 2.0 INGT165B / INGR165B Min. Typ. Max. Unit ...

Page 15

... IA E7, E8, E9, E10, F6, F7, F8, -- F9, F10, F11, H6, H7, H8, H9 VCC A0 A11, D9, L9, L11 VCC A1 H14, J11 -- Table 15: GigaSTaR 10/2003 - rev. 2.0 INGT165B / INGR165B Direction Active Description IN High Parallel data input, Bit 0 CMOS IN High Parallel data input, Bit 1 CMOS IN High Parallel data input, Bit 2 ...

Page 16

... N. C. VCC_A0 GND_D FLAGI VCC_A0 PDATA VALID VCC_ID [34] PDATA PERR# GND_ID N. C. [35] ® INGT165B Pin Assignments (Top View) INGT165B / INGR165B OSC VCC_A0 GND_A0 GND_A0 ...

Page 17

... INGR165B RECEIVER PIN DEFINITION Pin Name Pin # PDATA[0] A5 PDATA[1] B5 PDATA[2] A4 PDATA[3] B4 PDATA[4] A3 PDATA[5] B3 PDATA[6] A2 PDATA[7] B2 PDATA[8] B1 PDATA[9] C1 PDATA[10] D2 PDATA[11] E3 PDATA[12] D1 PDATA[13] E2 PDATA[14] E1 PDATA[15] F2 PDATA[16] G3 PDATA[17] G1 PDATA[18] H3 PDATA[19] H2 PDATA[20] J1 PDATA[21] J2 PDATA[22] L1 PDATA[23] K3 PDATA[24] K2 PDATA[25] M1 PDATA[26] L3 PDATA[27] M2 PDATA[28] N2 PDATA[29] P2 PDATA[30] N3 PDATA[31] P3 PDATA[32] N4 PDATA[33] ...

Page 18

... INGR165B RECEIVER PIN ASSIGNMENT (TOP VIEW PDATA PDATA PDATA [6] [4] [2] B PDATA PDATA PDATA PDATA [8] [7] [5] [3] C PDATA GND_D N. C. VCC_D [9] D PDATA PDATA VCC_D N. C. [12] [10] E PDATA PDATA PDATA N. C. [14] [13] [11] F VCC_D PDATA GND_D N. C. [15] ...

Page 19

... PACKAGE DIMENSIONS (12MM X 12MM PBGA) A Pitch Bottom View A1 Pin Corner A 10/2003 - rev. 2.0 INGT165B / INGR165B B A Side View A Top View Figure 15: Package Dimensions Pitch ∅ Ball C MILLIMETERS ± ± TYP. A 12.00 0.05 1.40 0.10 B 0.36 0.05 C Pitch 0.80 0.04 ∅ Ball 0.46 0. ...

Page 20

... At power-up and power-down sequences, all supply voltage nodes have to be ramped up and down with identical voltage ramping, otherwise the maximum rating of I can be exceeded and damage to the device may occur. 10/2003 - rev. 2.0 INGT165B / INGR165B (I/O Current DC or transient per pin ...

Page 21

... ORDERING CODE AND PRODUCTION STATUS INFORMATION Ordering Code Delivery package, minimum packing quantity (MPQ) INGT165B INGR165B INGSK Box containing 2 x INGT165B and 2 x INGR165B ING_TRC Piggyback Board w/ INGT165B and INGR165B, SUB D9 connector for cable data transmission ING_TRF Piggyback Board w/ INGT165B and INGR165B ...