DS1921H-F5 DALLAS [Dallas Semiconductor], DS1921H-F5 Datasheet - Page 22

DS1921H-F5

Manufacturer Part Number

DS1921H-F5

Description

Thermochron iButton

Manufacturer

DALLAS [Dallas Semiconductor]

Datasheet

1.DS1921H-F5.pdf

(40 pages)

DS1921L

the DS1921L and CRC16s at page boundaries until a reset pulse is issued. The Read Memory with CRC

command sequence can be ended at any point by issuing a reset pulse.

Clear Memory [3Ch]

The Clear Memory command is used to clear the Sample Rate, Mission Start Delay, Mission Time

Stamp, and Mission Samples Counter in the register page and the Temperature Alarm Memory and the

Temperature Histogram Memory. The memory must be cleared for the device to be set up for another

mission. For the Clear Memory command to function the EMCLR bit in Control Register must be set to

1. The Clear Memory command must be issued with the very next access to the device’s memory func-

tions (timed access). Issuing any other valid memory function command will reset the EMCLR bit. The

Clear Memory command takes approximately 500µs to complete and cannot be interrupted. However, it

is possible to issue a reset/presence sequence, execute any ROM command, and access the 4096 bits of

user-RAM or read the RTC or Status Register while the Clear Memory command is in progress. When

the Clear Memory command is completed the MEMCLR bit in the Status Register will read 1 and the

EMCLR bit will be 0.

Convert Temperature [44h]

If a mission is not in progress the Convert Temperature command can be issued to measure the current

temperature of the device. The result of the temperature conversion will be found at memory address

211h in the register page. This command takes approximately 300ms to complete and cannot be inter-

rupted. Memory access to any location of the device is possible while the temperature conversion takes

place.

1-WIRE BUS SYSTEM

The 1-Wire bus is a system that has a single bus master and one or more slaves. In all instances the

DS1921L is a slave device. The bus master is typically a microcontroller or PC. For small configurations

the 1-Wire communication signals can be generated under software control using a single port pin. For

multi-sensor networks, the DS2480B 1-Wire line driver chip or serial port adapters based on this chip

(DS9097U series) are recommended. This simplifies the hardware design and frees the microprocessor

from responding in real-time.

The discussion of this bus system is broken down into three topics: hardware configuration, transaction

sequence, and 1-Wire signaling (signal types and timing). The 1-Wire protocol defines bus transactions in

terms of the bus state during specific time slots that are initiated on the falling edge of sync pulses from

the bus master. For a more detailed protocol description, refer to Chapter 4 of the Book of DS19xx iButton

Standards.

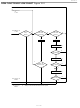

HARDWARE CONFIGURATION

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to

drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have open

drain or tri-state outputs. The 1-Wire port of the DS1921L is open-drain with an internal circuit

equivalent to that shown in Figure 11.

A multidrop bus consists of a 1-Wire bus with multiple slaves attached. At standard speed the 1-Wire bus

has a maximum data rate of 16.3kbits per second. The speed can be boosted to 142kbits per second by

activating the Overdrive mode. The DS1921L is not guaranteed to be fully compliant to the iButton

Standard. Its maximum data rate in standard speed mode is 14.1kbits per second and 125kbits per second

22 of 40