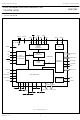

SAA7382GP Philips Semiconductors, SAA7382GP Datasheet - Page 8

SAA7382GP

Manufacturer Part Number

SAA7382GP

Description

Error correction and host interface IC for CD-ROM ELM

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7382GP.pdf

(60 pages)

Philips Semiconductors

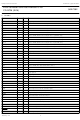

6.1

6.1.1

External memory address signals.

6.1.2

External memory RA16 signal if SRAM or, CAS signal if

DRAM.

6.1.3

External memory RA15 signal if SRAM or, RAS signal if

DRAM.

6.1.4

Write output enable signal for external buffer memory. This

is LOW when the SAA7382 wants to write data into the

external memory.

6.1.5

External buffer memory bidirectional data signals.

6.1.6

Frame sync for the Q-to-W subcode, indicates when

P-channel is available by a HIGH-to-LOW transition.

Frame 0 is also indicated by no transition on this line.

6.1.7

In response to SFSY going LOW data is clocked into the

SAA7382 before each rising edge using this clock output.

6.1.8

Q-to-W subcode is input in response to RCK in 3-wire EIAJ

mode or WS in “V4” mode compatible with the SAA7345.

6.1.9

Bit clock for the serial data input from the CD decoder.

6.1.10

Word clock for the serial data input from the CD decoder.

6.1.11

Serial data input from the CD decoder. This may be either

I

1996 Apr 25

2

S-bus or EIAJ 16-bit format.

Error correction and host interface IC for

CD-ROM (ELM)

Pin functions

RA0

RA16/CAS

RA15/RAS

RWE

RD0

SFSY

RCK

SUB

BCK

WS

DATA

TO

TO

RA14

RD7

8

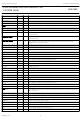

6.1.12

Error flag from the CD decoder. A HIGH indicates that a

byte has not been corrected by the C2 error corrector and

therefore is not valid. This is taken into account by the

SAA7382 error corrector.

6.1.13

Sub-CPU bidirectional data signal. This signal forms part

of the 3-wire serial interface between the SAA7382 and the

sub-CPU.

6.1.14

Sub-CPU sync signal. This signal forms part of the 3-wire

serial interface between the SAA7382 and the sub-CPU.

This signal is used to synchronize data transfers between

the sub-CPU and the SAA7382.

6.1.15

Sub-CPU interrupt signal. This active LOW output signals

to the sub-CPU that the SAA7382 has an interrupt request.

6.1.16

Forcing this input LOW resets the SAA7382.

6.1.17

Sub-CPU clock signal. This signal forms part of the 3-wire

serial interface between the SAA7382 and the sub-CPU.

This signal is the sub-CPU driven bit clock used to

synchronize the signals on the SDA line.

6.1.18

In the ATAPI mode this is the host chip select 1 address

signal. In the Sanyo and Oak compatibility modes setting

this input LOW enables the host interface.

6.1.19

This active LOW signal is the host write request.

6.1.20

This active LOW signal is the host read request.

C2PO

SDA

SCL

INT

RESET

SYN

CS1/HEN

HWR

HRD

Preliminary specification

SAA7382