ADM1041ARQ AD [Analog Devices], ADM1041ARQ Datasheet

ADM1041ARQ

Available stocks

Related parts for ADM1041ARQ

ADM1041ARQ Summary of contents

Page 1

PRODUCT FEATURES Digital calibration via internal EEPROM Supports SSI specification Comprehensive fault detection Reduced component count on secondary side Standalone or microcontroller control SECONDARY-SIDE FEATURES Generates error signal for primary-side PWM Output voltage adjustment and margining Current sharing Current limit ...

Page 2

ADM1041 TABLE OF CONTENTS Specifications..................................................................................... 6 Absolute Maximum Ratings.......................................................... 13 ESD Caution................................................................................ 13 Pin Configuration and Function Descriptions........................... 14 Terminology .................................................................................... 17 Theory of Operation ...................................................................... 19 Power Management.................................................................... 19 Gain Trimming and Configuration ......................................... 19 Differential Remote Sense Amplifier............................................ ...

Page 3

GENERAL DESCRIPTION The ADM1041 is a secondary-side and management IC specifi- cally designed to minimize external component counts and to eliminate the need for manual calibration or adjustment on the secondary-side controller. The principle application of this ...

Page 4

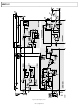

ADM1041 Figure 3. Chip Diagram, Part 1 Rev Page ...

Page 5

Figure 4. Chip Diagram, Part 2 Rev Page ADM1041 ...

Page 6

ADM1041 SPECIFICATIONS T = –40 to +85° ± 10%, unless otherwise noted Table 1. Parameter SUPPLIES Current Consumption Peak I during EEPROM Erase Cycle DD, UNDERVOLTAGE LOCKOUT, ...

Page 7

Parameter LOCAL VOLTAGE SENSE AND FALSE UV CLAMP 3 Input Voltage Range Stage Gain False UV Clamp Input Voltage Nominal, LS and Trim Range Clamp Trim Step Clamp Trim Step Local Overvoltage Nominal and Trim ...

Page 8

ADM1041 Parameter DC Offset Trim Range (with respect to input) DC Offset Trim Step Size (with respect to input) CURRENT SENSE CALIBRATION 2 Total Current Sense Error (Gain and Offset) Gain Range (I ) SENSE Gain Setting 1 (Reg 16h[2:0] ...

Page 9

Parameter CURRENT LIMIT ERROR AMPLIFIER 2 Current Limit Trim Range Current Limit Trim Step Current Limit Trim Step Transconductance Output Source Current Output Sink Current CURRENT SHARE DRIVER 6 Output Voltage Short Circuit Source Current Source Current Sink Current CURRENT ...

Page 10

ADM1041 Parameter Reverse Voltage Detector Turn-Off Threshold Reverse Voltage Detector Turn-On Threshold FD Input Impedance FS Input Impedance AC 1/AC 2 COMPARATOR SENSE SENSE (AC or Bulk Sense) Threshold Voltage Threshold Adjust Range Threshold Trim Step Hysteresis Adjust Range Hysteresis ...

Page 11

Parameter OVP Noise Filter UVP Noise Filter PSON 7 8 Input Low Level 8 Input High Level Debounce 7 7 PEN , DC_OK , CBD, AC_OK Open-Drain N-Channel Option 8 Output Low Level = On Open-Drain P-Channel Output High Level ...

Page 12

ADM1041 1 This specification is a measure of I during an EEPROM page erase cycle. The current is a dynamic. Refer to Figure 29 for a typical I DD erase. 2 Specification is not production tested, but is supported by ...

Page 13

ABSOLUTE MAXIMUM RATINGS Table 2. Parameter Supply Voltage (Continuous Data Pins SDA, SCL, V DATA Continuous Power at 25°C, P D-QSOP24 Operating Temperature, T AMB Junction Temperature Storage Temperature, T STG Lead Temperature (Soldering, 10 Seconds), ...

Page 14

ADM1041 PIN CONFIGURATION AND FUNCTION DESCRIPTIONS Table 3. Pin Function Descriptions Pin No. Mnemonic Description 1 V Positive Supply for the ASIC. Normal range is 4 5.5 V. Absolute maximum rating is 6 ...

Page 15

Pin No. Mnemonic Description 10 AC 2/MON2 AC/Bulk Sense Input 2 or Monitor 2 Input. SENSE AC that used for the OrFET. It also allows dc and opto-coupled signals that are not suitable for the OrFET control. MON2: When MON2 ...

Page 16

ADM1041 Pin No. Mnemonic Description This pin is the positive remote load voltage sense input and is normally divided down from the power S supply output voltage to 2 load using an external voltage ...

Page 17

TERMINOLOGY Table 5. Mnemonic Description POR Power-On Reset. When V the logic into a state that allows a clean start-up. UVL Undervoltage Lockout. This is used CVMode Constant Voltage Mode. This is the normal mode of ...

Page 18

ADM1041 Mnemonic Description Pulse_OK As well as providing ac sense, the preceding connection to the transformer is used to gate the operation of the OrFET circuit. If the output of the transformer is good and has no problems, the OrFET ...

Page 19

THEORY OF OPERATION POWER MANAGEMENT This block contains V undervoltage lockout circuitry and a DD power-on/reset function. It also provides precision references for internal use and a buffered reference voltage, V configured to an output pin, overloading, shorting to ground, ...

Page 20

ADM1041 DIFFERENTIAL REMOTE SENSE AMPLIFIER This amplifier senses the load voltage and is the main voltage feedback input. A differential input is used to compensate for the voltage drop on the negative output cable of the power supply. An external ...

Page 21

VOLTAGE (V) Figure 10. Current Limit 2.75 2.50 2.25 2.00 1.75 1.50 1.25 1.00 0.75 0.50 0. 100 1k 10k 100k 1M BANDWIDTH Figure 11. ...

Page 22

ADM1041 CURRENT SENSING Current is typically sensed by a low value resistor in series with the positive output of the power supply, just before the OrFET or diode. For high voltages (12 V and higher), this resistor is usually placed ...

Page 23

Figure 13. Current Sense Rev Page ADM1041 ...

Page 24

ADM1041 CURRENT SHARE The current share method is the master–slave type, which means that the power supply with the highest output current automatically becomes the master and controls the share bus signal. All other power supplies become slaves, and the ...

Page 25

Figure 14. Current Share Circuit and Soft-start Rev Page ADM1041 ...

Page 26

ADM1041 SHARE 1V OFFSET 100% I OUT Figure 15. Load Share Characteristic Rev Page ...

Page 27

PULSE/AC 2 SENSE When configured, PULSE and AC monitor the output of SENSE the power main transformer. See Figure 16. PULSE Providing the output of the pulse function (PULSE_OK) is high, the FET in the ORing circuit can be turned ...

Page 28

ADM1041 OrFET GATE DRIVE When configured, this block provides a signal to turn on/off an OrFET used in the output of paralleled power supplies. The gate drive voltage of one of these FETs is typically ...

Page 29

T = 222ns TOTAL Figure 19. OrFET Turn- Off Time (Inverse Polarity) CURRENT PULSEOK LOADOK REVERSEOK RESET VOLTAGE DETECTOR Figure 20. OrFET Turn-On Time (Inverse Polarity +10V OUT PENOK OrFET OK POLARITY V ...

Page 30

ADM1041 OSCILLATOR AND TIMING GENERATORS An on-board oscillator is used to generate timing signals. Some trimming of the oscillator is provided to adjust for variations in processing. All timing generated from the oscillator is expected to meet the same tolerances ...

Page 31

AC_OK This output is true when either SENSE (configurable). It can be configured as an open-drain N-channel or P-channel MOSFET and as positive or negative (inverted) logic. A pull-up or pull-down resistor is required. This pin ...

Page 32

ADM1041 Figure 24. General Logic Rev Page ...

Page 33

SMBus SERIAL PORT The programming and microprocessor interface for the ADM1041 is a standard SMBus serial port, which consists of a clock line and a data line. The more rigorous requirements of the SMBus standard are specified in order to ...

Page 34

ADM1041 BROADCASTING In a power supply with multiple outputs recommended that all outputs rise together. Because the SMBus is relatively slow, simply writing sequentially to the PSON signal in each ADM1041, for instance, causes a significant delay in ...

Page 35

SCLK SDATA START BY MASTER SERIAL BUS ADDRESS BYTE Figure 25. Writing a Register Address to the Address Pointer Register, then Writing Data to the Selected Register 1 9 SCLK SDATA START ...

Page 36

ADM1041 SMBus PROTOCOLS FOR RAM AND EEPROM The ADM1041 contains volatile registers (RAM) and nonvola- tile EEPROM. RAM occupies the address locations from 00h to 7Fh, while EEPROM occupies the address locations from 8000h to 813Fh. The SMBus specification defines ...

Page 37

In the ADM1041, the send byte protocol is used to write a register address to RAM for a subsequent single-byte read from the same address or block read or write starting at that address. This is illustrated in Figure 30. ...

Page 38

ADM1041 6. The master sends a data byte that tells the slave device how many data bytes will be sent. The SMBus specification allows a maximum of 32 data bytes to be sent in a block write. 7. The slave ...

Page 39

Notes on SMBus Read Operations The SMBus interface of the ASIC cannot load the SMBUS if no power is applied to the ASIC. This requirement allows a power supply to be disconnected from the ac supply while still installed in ...

Page 40

ADM1041 EXTENDED SMBus ADDRESSING A potential problem exists when using more than three ADM1041s in a single power supply. The first time the device is powered up, Bit 1 of Configuration Register 1 (ADD1 This means that only ...

Page 41

REGISTER LISTING Table 8. Register Address Name 00h/2Ah Status1/Status1 Mirror Latched 01h/2Bh Status2/Status2 Mirror Latched 02h/2Ch Status3/Status3 Mirror Latched 03h Calibration Bits 04h Current Sense CC 05h Current Share Offset 06h Current Share Slope 07h EEPROM_lock 08h Load OV Fine ...

Page 42

ADM1041 DETAILED REGISTER DESCRIPTIONS Table 9. Register 00h, Status1. Power-On Default XXh (Refer to the logic schematic—Figure 24.) Bit No. Name R/W 7 ovfault R 6 uvfault R 5 ocpto R 4 mfg1 R 3 mfg2 R 2 mfg3 R ...

Page 43

Bit No. Name R/W 1–0 loadov_recover R/W Table 13. Register 04h, Current Sense CC. Power-On Default from EEPROM Register 8104h during Power-Up. Bit No. Name R/W 7–3 curr_limit R/W 2 Share_OK_Window 1–0 Share_OK_thresh R/W Table 14. Register 05h, Current Share ...

Page 44

ADM1041 Table 19. Register 0Ah, Local OVP Trim. Power-On Default from EEPROM Register 810Ah during Power-Up. Bit No. Name R/W 7–0 local_ovp R/W Table 20. Register 0Bh, OTP Trim. Power-On Default from EEPROM Register 810Bh during Power-Up. Bit No. Name ...

Page 45

Table 23. Register 0Eh, Config2. Power-On Default from EEPROM Register 810Eh during Power-Up. Bit No. Name R/W 7–5 mn2s2, mn2s1, mn2s0 W 4–2 mn3s2, mn3s1, R/W mn3s0 1–0 pokts1, pokts0 R/W Description option iopin ...

Page 46

ADM1041 Table 24. Register 0Fh, Config3. Power-On Default from EEPROM Register 810Fh during Power-Up. Bit No. Name R/W 7–5 mn4s2, mn4s1, R/W mn4s0 4–2 mn5s2, mn5s1, R/W mn5s0 1–0 psonts1, psonts0 R/W Table 25. Register 10h, Config4. Power-On Default from ...

Page 47

Bit No. Name R/W 3–2 ssrs1, ssrs0 R/W 1 add1 R/W 0 trim_lock R/W Table 26. Register 11h, Config5. Power-On Default from EEPROM Register 8111h 8110h during Power-Up. Bit No. Name R/W 7 curr_lim_dis R/W 6 polpen0 R/W 5 polcbd0 ...

Page 48

ADM1041 Bit No. Name R/W 7 polpen1 R/W 6 polcbd1 R/W 5 polDC_OK1 R/W 4 polAC_OK1 R/W 3 polfg R/W 2 m_shr_clmp (W) 1 m_cbd_w R/W 0 m_cbd_clr R/W Table 29. Register 14h, Current Sense Divider Error Trim 1. Power-On ...

Page 49

Table 32. Register 17h, Current Sense Option 2. Power-On Default from EEPROM Register 8117h during Power-Up. Bit No. Name R/W 7 csense_mode R/W 6 chopper R/W 5 ct_range R/W 4 select_gnd_offset R/W 3 Reserved X 2–0 os_dc_range R/W Table 33. ...

Page 50

ADM1041 Table 36. Register 1Bh, Sel CBD/SMBAlert2. Power-On Default from EEPROM Register 811Bh during Power-Up. Bit No. Name R/W 7 selcbd2 <7> R/W 6 selcbd2 <6> R/W 5 selcbd2 <5> R/W 4 selcbd2 <4> R/W 3 selcbd2 <3> R/W 2 ...

Page 51

Table 40. Register 2Bh, Status2 Mirror. Power-On Default 00h. These flags are cleared by a register read, provided the fault no longer persists. Bit No. Name R/W 7 Share_OKb_L R 6 orfetokb_L R 5 reverseokb_L b_L ...

Page 52

ADM1041 MICROPROCESSOR SUPPORT Table 43. Mnemonic Description m_pson_r Allows the microprocessor to read the state of PSON. This allows only one ADM1041 to be configured as the PSON interface to the host system. m_pson_w Allow the microprocessor to write to ...

Page 53

Mnemonic Description ocpf If this flag is high, an overcurrent has been sensed and the ocp timer has started. m_DC_OK_r This flag indicates the status of the DC_OK pin. m_psonok_r This flag indicates the status of the PS m_penok_r This ...

Page 54

ADM1041 TRIM TABLE This table shows all of the trims that can be set in the ADM1041. Table 44. Description Set Load Voltage. Trim output from differential amplifier to set voltage at load. Set Load OV. Trim calibrated output from ...

Page 55

APPENDIX A—CONFIGURATION TABLE This table is included for users to program the part by function, rather than by register. Table 45. Description Bit No. Chip address is 1010xxx. Second address bit (EEPROM programmable). 1 First address bit: ADD0 = L, ...

Page 56

ADM1041 Description Bit No. Trim registers, locking bit. 0 Current Sense Mode. 7 Chopper Mode. 6 Current sense dc offset adjustment (with respect to the input). 2–0 Compensates for the amplifier input offset voltage. Current sense external divider error correction ...

Page 57

Description Bit No. Option: Pulse/AC 1/MON1. 3–1 SENSE Option: AC 2/MON SENSE 7–5 Option: PSON/MON3 4–2 Option: DC_OK/MON4 7–5 Name Bit Bit Bit mn1s2 mn1s1 mnls0 ...

Page 58

ADM1041 Description Bit No. To set DC_OK polarity, see polDC_OK. Option: V /AC_OK/MON5. 4–2 REF To set AC_OK polarity, see polDC_OK. AC sense source. 2 PSON delay/debounce time. 1–0 DC_OK on delay. 1–0 Delay time from dc outputs being enabled ...

Page 59

Description Bit No. Current share capture range. 5–4 Maximum output voltage control range due to the current share action. Soft-start mode provides 2 option for soft-startramp to be gated by acsnsok Soft-start step rise time 3–2 (output rise time) PEN ...

Page 60

ADM1041 Description Bit No. Set CBD Output Polarity 5 6 Set OrFET Gate Drive 3 Polarity This is an open-drain N-FET Set DC_OK Output Polarity. 5 Also selects open-drain 5 N-channel or P-channel. Set I Clamp Release 0 SHARE threshold. ...

Page 61

APPENDIX B—TEST NAME TABLE This table is included for ADI’s internal reference use This is a cross reference for the ADI test program. Table 46. Specification Supplies Current Consumption DD Peak I during EEPROM Erase Cycle ...

Page 62

ADM1041 Specification SHARE BUS OFFSET Current Share Offset Range Zero Current Offset Trim Step CURRENT TRANSFORMER SENSE INPUT Gain Setting 0 Gain Setting 1 CT Input Sensitivity (Gain Set 0) CT Input Sensitivity (Gain Set 1) Input Impedance Source Current ...

Page 63

Specification DC_OK DC_OK, On Delay (Power-On and OK Delay) DC_OK, Off Delay (Power-Off Early Warning) SMBus, SDL/SCL Input Voltage Low Input Voltage High Output Voltage Low Pull-Up Current Leakage Current ADD0, HARDWIRED ADDRESS BIT ADD0 Low Level ADD0 Floating ADD0 ...

Page 64

... Temperature Range ADM1041ARQ −40°C to +85°C ADM1041ARQ-REEL −40°C to +85°C ADM1041ARQ-REEL7 −40°C to +85°C 2 Purchase of licensed I C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I Rights to use these components ...