NBSG86ABAHTBG ON Semiconductor, NBSG86ABAHTBG Datasheet - Page 2

NBSG86ABAHTBG

Manufacturer Part Number

NBSG86ABAHTBG

Description

IC CLOCK/DATA DIFF DIV/2 16FCBGA

Manufacturer

ON Semiconductor

Datasheet

1.NBSG86AMNHTBG.pdf

(14 pages)

Specifications of NBSG86ABAHTBG

Logic Type

Configurable Multiple Function

Number Of Circuits

2

Number Of Inputs

2

Schmitt Trigger Input

No

Output Type

Differential

Voltage - Supply

2.375 V ~ 3.465 V

Operating Temperature

-40°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

16-FCBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Output High, Low

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

NBSG86ABAHTBG

Manufacturer:

ON Semiconductor

Quantity:

10 000

Table 1. Pin Description

1. In the differential configuration when the input termination pins (VTDx, VTDx, VTSEL) are connected to a common termination voltage,

2. All V

3. When an output level of 400 mV is desired and V

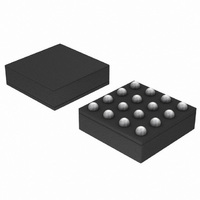

BGA

N/A

C2

C1

B1

B2

A1

A2

A3

A4

B3

B4

C4

C3

D4

D3

D2

D1

and if no signal is applied then the device will be susceptible to self−oscillation.

Pin

CC

QFN

10

12

13

14

15

16

11

1

2

3

4

5

6

7

8

9

−

Figure 1. BGA−16 Pinout (Top View)

and V

C

D

A

B

(Note 3)

EE

VTSEL

Name

VTD1

VTD1

VTD0

VTD0

OLS

SEL

SEL

V

V

VTD1

VTD0

D1

D1

D0

D0

EP

Q

Q

pins must be externally connected to Power Supply to guarantee proper operation.

1

SEL

SEL

CC

EE

VTSEL

OLS

ECL, CML, LVCMOS,

ECL, CML, LVCMOS,

ECL, CML, LVCMOS,

ECL, CML, LVCMOS,

ECL, CML, LVCMOS,

ECL, CML, LVCMOS,

2

D1

D0

LVDS, LVTTL Input

LVDS, LVTTL Input

LVDS, LVTTL Input

LVDS, LVTTL Input

LVDS, LVTTL Input

LVDS, LVTTL Input

RSECL Output

RSECL Output

Input

V

V

I/O

D1

D0

3

CC

−

−

−

−

−

−

−

−

EE

VTD1

VTD0

4

Q

Q

CC

Input Pin for the Output Level Select (OLS). See Table 2.

Inverted Differential Select Logic Input.

Noninverted Differential Select Logic Input.

Common Internal 50 W Termination Pin for SEL/SEL. See Table 7. (Note 1)

Internal 50 W termination pin. See Table 7. (Note 1)

Noninverted Differential Input 1. Internal 75 kW to V

Inverted Differential Input 1. Internal 75 kW to V

Internal 50 W Termination Pin. See Table 7. (Note 1)

Positive Supply Voltage (Note 2)

Noninverted Differential Output. Typically Terminated with 50 W Resistor to

V

Inverted Differential Output. Typically Terminated with 50 W Resistor to

V

Negative Supply Voltage (Note 2)

Internal 50 W Termination Pin. See Table 7. (Note 1)

Inverted Differential Input 0. Internal 75 kW to V

Noninverted Differential Input 0. Internal 75 kW to V

Internal 50 W Termination Pin. See Table 7. (Note 1)

The Exposed Pad (EP) and the QFN−16 package bottom is thermally connected

to the die for improved heat transfer out of package. The exposed pad must be

attached to a heat−sinking conduit. The pad is not electrically connected to the

die but may be electrically and thermally connected to V

− V

TT

TT

http://onsemi.com

EE

= V

= V

> 3.0 V, 2 kW resistor should be connected from OLS pin to V

CC

CC

− 2 V.

− 2 V

2

VTSEL

OLS

SEL

SEL

Figure 2. QFN−16 Pinout (Top View)

1

2

3

4

VTD1

VTD0 D0

16

5

Description

NBSG86A

15

D1

6

D0 VTD0

14

D1 VTD1

7

EE

EE

and 36.5 kW to V

and 36.5 kW to V

EE

EE

13

8

.

.

EE

on the PC board.

12

10

11

9

V

Q

Q

V

EE

CC

CC

CC

Exposed Pad

(EP)

EE

.

.

.