LCMXO2-256HC-4SG32IES Lattice, LCMXO2-256HC-4SG32IES Datasheet - Page 71

LCMXO2-256HC-4SG32IES

Manufacturer Part Number

LCMXO2-256HC-4SG32IES

Description

FPGA - Field Programmable Gate Array 256 LUTs 22 I/O 3.3V engineering sample

Manufacturer

Lattice

Datasheet

1.LCMXO2-256HC-4SG32I.pdf

(106 pages)

Specifications of LCMXO2-256HC-4SG32IES

Rohs

yes

Maximum Operating Frequency

269 MHz

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Package / Case

QFN-32

Minimum Operating Temperature

- 40 C

- Current page: 71 of 106

- Download datasheet (8Mb)

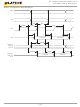

sysCLOCK PLL Timing (Continued)

t

1. Period jitter sample is taken over 10,000 samples of the primary PLL output with a clean reference clock. Cycle-to-cycle jitter is taken over

2. Output clock is valid after t

3. Using LVDS output buffers.

4. CLKOS as compared to CLKOP output for one phase step at the maximum VCO frequency. See TN1199,

5. At minimum f

6. Maximum allowed jitter on an input clock. PLL unlock may occur if the input jitter exceeds this specification. Jitter on the input clock may be

7. Edge Duty Trim Accuracy is a percentage of the setting value. Settings available are 70 ps, 140 ps, and 280 ps in addition to the default

8. Jitter values measured with the internal oscillator operating. The jitter values will increase with loading of the PLD fabric and in the presence

ROTATE_WD

Parameter

1000 cycles. Phase jitter is taken over 2000 cycles. All values per JESD65B.

Design and Usage Guide

transferred to the output clocks, resulting in jitter measurements outside the output specifications listed in this table.

value of none.

of SSO noise.

PFD.

PHASESTEP Pulse Width

As the f

PFD

for more details.

LOCK

increases the time will decrease to approximately 60% the value listed.

for PLL reset and dynamic delay adjustment.

Descriptions

Over Recommended Operating Conditions

3-32

Conditions

DC and Switching Characteristics

MachXO2 Family Data Sheet

Min.

4

MachXO2 sysCLOCK PLL

Max.

—

VCO Cycles

Units

Related parts for LCMXO2-256HC-4SG32IES

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 22 I/O 3.3V -6 Speed

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 22 I/O 3.3V -6 Speed

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 4 SPEED

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 4 SPEED

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 22 I/O 3.3V -5 Speed

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 22 I/O 3.3V -4 Speed

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 22 I/O 3.3V -6 Speed

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 45 I/O 3.3V 4 SPEED

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 6 SPEED

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 5 SPEED

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 5 SPEED

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 4 SPEED

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 45 I/O 3.3V 6 SPEED

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 5 SPEED

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 256 LUTs 56 I/O 3.3V 4 SPEED

Manufacturer:

Lattice