FOD2200 Fairchild Optoelectronics Group, FOD2200 Datasheet

FOD2200

Specifications of FOD2200

FOD2200FS

FOD2200_NL

FOD2200_NL

Available stocks

Related parts for FOD2200

FOD2200 Summary of contents

Page 1

... CMOS logic and result in lower power consumption compared to other high speed opto-couplers. Logic signals are transmitted with a maximum propagation delay of 300ns. The FOD2200 is useful for isolating high speed logic interfaces, buffering of input and output lines, and implementing isolated line receivers in high noise environments ...

Page 2

... EH T Operating Temperature A N Fan Out (TTL Load) *The initial switching threshold is 1.6mA or less recommended that 2.2mA be used to permit at least a 20% CTR degradation guardband. ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0 25°C unless otherwise specified) A Parameter Parameter 2 Value Units -40 to +125 ° ...

Page 3

... Common Mode Transient Immunity H (at Output High Level) |CM | Common Mode L Transient Immunity (at Output Low Level) *Typical values 25° ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0 0°C to +85° 4.5V to 20V 0.1mA unless otherwise specified.) F(OFF) Test Conditions I = 5mA 10µA R Pins 2 & ...

Page 4

... V < 0.8V). OUT 9. Device considered a two-terminal device: Pins and 4 shorted together, and Pins and 8 shorted together. 10. Duration of output short circuit time should not exceed 10ms. ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0.2 (Continued) = 0°C to +85° 4.5V to 20V Test Conditions ...

Page 5

... Test Circuits INPUT MONITORING NODE Fig. 1. Test Circuit and Waveforms for t Fig. 2. Test Circuit and Waveforms for t ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0 PULSE GEN OUTPUT 100 kHz MONITORING 10 % DUTY NODE FOD2200 CYCLE GND 120 pF THE PROBE AND JIG CAPACITANCES ...

Page 6

... Figure 4. Recommended LSTTL to LSTTL Circuit V (+5 V) CC1 1.1k 1 DATA 2 INPUT D1 TTL OR 3 LSTTL 4 D1 (1N4150) REQUIRED FOR ACTIVE PULL-UP DRIVER. Figure 6. Recommended LED Drive Circuit *The 120pF capacitor may be omitted in applications where 500ns propagation delay is sufficient. ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0 FOD2200 ...

Page 7

... I = 3mA PHL F PHL 140 t PLH 100 60 -40 - – AMBIENT TEMPERATURE ( C) A ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0.2 Figure 9. Output Voltage vs. Input Forward Current - 0.0 1.4 1.5 1.6 1.7 Figure 11. Logic Low Output Voltage vs. Ambient Temperature 0.8 0.7 0.6 0.5 ...

Page 8

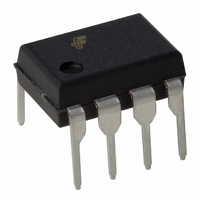

... MIN 0.022 (0.56) 0.016 (0.41) 0.100 (2.54) TYP Lead Coplanarity : 0.004 (0.10) MAX Note: All dimensions are in inches (millimeters) ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0.2 0.4" Lead Spacing 0.200 (5.08) 0.140 (3.55) 15 MAX 0.300 (7.62) TYP 0.022 (0.56) 0.016 (0.41) 8-Pin DIP – ...

Page 9

... SDV Marking Information Definitions ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0.2 Example Part Number FOD2200 Standard Through Hole FOD2200S Surface Mount Lead Bend FOD2200SD Surface Mount; Tape and Reel FOD2200T 0.4" Lead Spacing FOD2200V VDE0884 FOD2200TV VDE0884; 0.4” Lead Spacing FOD2200SV VDE0884 ...

Page 10

... Reflow Profile 300 250 200 150 100 50 0 ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0 User Direction of Feed Description Tape Width Tape Thickness Sprocket Hole Pitch Sprocket Hole Diameter Sprocket Hole Location Pocket Location Pocket Pitch Pocket Dimensions Cover Tape Width Cover Tape Thickness Max ...

Page 11

... Datasheet Identification Product Status Advance Information Form ative / In Design Preliminary First Production No Identification Needed Full Production Obsolete Not In Production ©2004 Fairchild Semiconductor Corporation FOD2200 Rev. 1.0.2 ® * Power-SPM™ ® PowerTrench PowerXS™ ® Programmable Active Droop™ ® SM QFET QS™ ...