ATA6622-EK Atmel, ATA6622-EK Datasheet - Page 4

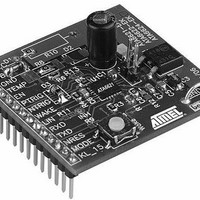

ATA6622-EK

Manufacturer Part Number

ATA6622-EK

Description

BOARD DEMO LIN SBC FOR ATA6622

Manufacturer

Atmel

Specifications of ATA6622-EK

Main Purpose

Interface, LIN

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

ATA6622

Primary Attributes

LIN-SBC (System-Basis-Chip) Transceiver, LIN 2.0, Voltage Regulator, Window Watchdog

Secondary Attributes

4 Power Modes: Pre-Normal, Normal, Sleep, Silent, 20-QFN

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

3. Functional Description

3.1

3.2

3.3

3.4

3.5

3.6

4

Physical Layer Compatibility

Supply Pin (VS)

Ground Pin (GND)

Voltage Regulator Output Pin (VCC)

Voltage Regulator Sense Pin (PVCC)

Bus Pin (LIN)

Atmel ATA6622/ATA6624/ATA6626

Since the LIN physical layer is independent from higher LIN layers (e.g., the LIN protocol

layer), all nodes with a LIN physical layer according to revision 2.x can be mixed with LIN

physical layer nodes, which, according to older versions (i.e., LIN 1.0, LIN 1.1, LIN 1.2, LIN

1.3), are without any restrictions.

The LIN operating voltage is V

disable data transmission if V

After switching on VS, the IC starts in Fail-safe Mode, and the voltage regulator is switched on.

The supply current is typically 10µA in Sleep Mode and 57µA in Silent Mode.

The IC does not affect the LIN Bus in the event of GND disconnection. It is able to handle a

ground shift up to 11.5% of VS. The mandatory system ground is pin 5.

The internal 3.3V/5V voltage regulator is capable of driving loads up to 85mA. It is able to sup-

ply the microcontroller and other ICs on the PCB and is protected against overloads by means

of current limitation and overtemperature shut-down. Furthermore, the output voltage is moni-

tored and will cause a reset signal at the NRES output pin if it drops below a defined threshold

V

base connected to the VCC pin and its emitter connected to PVCC.

The PVCC is the sense input pin of the 3.3V/5V voltage regulator. For normal applications

(i.e., when only using the internal output transistor), this pin is connected to the VCC pin. If an

external boosting transistor is used, the PVCC pin must be connected to the output of this

transistor, i.e., its emitter terminal.

A low-side driver with internal current limitation and thermal shutdown and an internal pull-up

resistor compliant with the LIN 2.x specification are implemented. The allowed voltage range

is between –27V and +40V. Reverse currents from the LIN bus to VS are suppressed, even in

the event of GND shifts or battery disconnection. LIN receiver thresholds are compatible with

the LIN protocol specification. The fall time from recessive to dominant bus state and the rise

time from dominant to recessive bus state are slope controlled.

thun

. To boost up the maximum load current, an external NPN transistor may be used, with its

S

S

falls below VS

= 5V to 27V. An undervoltage detection is implemented to

th

< 4V in order to avoid false bus messages.

4986J–AUTO–03/11