IRDC3710-DF International Rectifier, IRDC3710-DF Datasheet

IRDC3710-DF

Related parts for IRDC3710-DF

IRDC3710-DF Summary of contents

Page 1

WIDE INPUT AND OUTPUT, SYNCHRONOUS BUCK REGULATOR FEATURES Input Voltage Range 28V Output Voltage Range: 0.5V to 12V Constant On-Time control Excellent Efficiency at very low output current levels Gate drive charge pump option to maximize efficiency at ...

Page 2

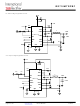

Fix Gate Voltage Application Circuit: V3.3 6.2k 10k R ISET 3.3V Input Voltage Application Circuit: V3.3 6.2k 10k R ISET Page www.irf.com V5 D BOOT R NC CPO PVCC FF BOOT UGATE VCC C BOOT IR3710 EN ...

Page 3

ABSOLUTE MAXIMUM RATINGS Absolute Maximum Ratings (Referenced to GND) BOOT Voltage: ................................................40 V PHASE Voltage:....-5V(100ns),-0.3V(DC) to 32.5 V FF, ISET:..........................................................32 V BOOT minus PHASE Voltage:........................7.5 V PVCC: ............................................................7.5 V VCC:................................................................3.9 V PGOOD:..........................................................3.9 V PGND to GND:................................... -0.3V to 0.3V All ...

Page 4

PARAMETER NOTE FAULT PROTECTION ISET pin output current Under Voltage Threshold Under Voltage Hysteresis Over Voltage Threshold PGOOD Delay Threshold ( GATE DRIVE UGATE Source Resistance 1 UGATE Sink Resistance 1 UGATE Rise and Fall Time LGATE Source ...

Page 5

IC PIN ORDER AND DESCRIPTION NAME NUMBER I/O LEVEL BOOT 1 V +PVCC 3.3V ISET 4 32V PGOOD 5 3.3V GND 6 Reference FCCM 3.3V VCC ...

Page 6

BLOCK DIAGRAM VCC Charge CPO Pump Regulator PGND x0.8 - Run SOFT V REF START GND x1.2 EN PVCC Page www.irf.com PVCC FF FCCM PVCC FF ZCROSS Run PWM ...

Page 7

TYPICAL OPERATING DATA (Circuit of Figure 18, VCC = 3.3V 5V, V 1000000 1000000 1000 1000 , , Rff 0.5 fsw Rff 0.5 fsw ( ( ) ) , , Rff 1 fsw Rff 1 fsw ( ( ...

Page 8

TYPICAL OPERATING WAVEFORM (Circuit of Figure 18, VCC = 3.3V 5V, V CH1:Vout(0.5V/div), CH2: PHASE (20V/div) CH3: PGOOD(5V/div), CH4:EN(5V/div) ; 50uS/div Figure 7. Start up with FCCM = Low @ 30mA CH1:Vout(0.5V/div), CH2: PHASE (20V/div) CH3: PGOOD(5V/div), CH4:EN(5V/div) ...

Page 9

CH1:Vout(50mV/div), CH2: PHASE (5V/div);50uS/div Figure 12. Frequency Variation less than 10% at 20A Load CH1:Vout(50mV/div), CH3: Inductor Current (10A/div), CH4: On-Board Load: 0A-14A ;50uS/div Figure 13. Load Step Transient in CCM @ Vin = 19V CH1:Vout(50mV/div), CH3: Inductor Current (10A/div), ...

Page 10

TYPICAL OPERATING CIRCUIT V5 BAT54S D2 D1 CPO V3.3 1uF VCC EN FCCM PGOOD ISET 5.11K SS 56pF 2.2nF Figure 18. Typical Application Circuit for 24A Load Page www.irf.com V IN BAT54T 180K PVCC FF BOOT IRF6721 ...

Page 11

FUNCTIONAL DESCRIPTION Refer to Block Diagram ON-TIME GENERATOR The PWM comparator initiates a SET signal (PWM pulse) when the FB pin falls below lower of the reference (VREF) or soft start (SS) voltage. The PWM on-time duration is programmed with ...

Page 12

CHARGE PUMP The purpose of the charge pump is to improve the system efficiency. A combination of VCC, V5 and three(3) external components are used to boost PVCC PVCC drives the synchronous CP TH MOSFET and ...

Page 13

... By combining the P and P , the total switching SW Qrr power loss of the upper MOSFETs is much greater than its conduction loss. International Rectifier MOSFET datasheets has separated the gate charge of Q and Q so that the designer can calculate GS1 GS2 the switching power loss. Therefore, selection of the upper MOSFETs should consider those factors ...

Page 14

The voltage rating of the input capacitor needs to be greater than the maximum input voltage because of the high frequency ringing at the phase node. The typical percentage is 25%. Output Capacitor Selection Select the output capacitor involves meeting ...

Page 15

DESIGN EXAMPLE Design Criteria: Input Voltage 21V IN Output Voltage 1.1V OUT Switching Frequency 300KHz S Inductor Ripple Current, Δ Maximum Output Current 20A OUT Over Current ...

Page 16

Gate Impedance: We recommended placing LGATE signal path on top next to the source of low side MOSFET path and place UGATE signal path on top of PHASE signal path. If the connection of PGND pin to the source of ...

Page 17

PCB PAD AND COMPONENT PLACEMENT Figure 25. Ssuggested pad and component placement. Page www.irf.com IR3710MTRPBF IR Confidential 4/26/10 ...

Page 18

SOLDER RESIST Figure 26. Suggested solder resist placement. Page www.irf.com IR3710MTRPBF IR Confidential 4/26/10 ...

Page 19

STENCIL DESIGN Page www.irf.com Figure 27. Suggested stencil design. IR Confidential IR3710MTRPBF 4/26/10 ...

Page 20

PACKAGE INFORMATION IR WORLD HEADQUATERS: 233 Kansas St, EL Segundo, California 90245, USA Tel: (310)-252-7105 Page www.irf.com Figure 28. Package Outline Drawing Data and specifications subject to change without notice. This product has been designed and qualified ...