C8051F342-GQ Silicon Laboratories Inc, C8051F342-GQ Datasheet - Page 185

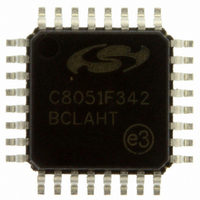

C8051F342-GQ

Manufacturer Part Number

C8051F342-GQ

Description

IC 8051 MCU FLASH 64K 32LQFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F34xr

Datasheets

1.C8051F349-GQ.pdf

(276 pages)

2.C8051F342-GQ.pdf

(1 pages)

3.C8051F347-GQ.pdf

(296 pages)

Specifications of C8051F342-GQ

Program Memory Type

FLASH

Program Memory Size

64KB (64K x 8)

Package / Case

32-LQFP

Core Processor

8051

Core Size

8-Bit

Speed

48MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART, USB

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Ram Size

4.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 21x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

5.25 KB

Interface Type

I2C/SMBus/SPI/UART/USB

Maximum Clock Frequency

48 MHz

Number Of Programmable I/os

25

Number Of Timers

4

Operating Supply Voltage

2.7 V to 5.25 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

KSK-SL-F34X, KSK-SL-TOOLSTICK, PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F340DK

Minimum Operating Temperature

- 40 C

On-chip Adc

17-ch x 10-bit

No. Of I/o's

25

Ram Memory Size

4352Byte

Cpu Speed

48MHz

No. Of Timers

4

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1748 - ADAPTER TOOLSTICK FOR C8051F34X336-1482 - DAUGHTER CARD TOOLSTCK C8051F342770-1006 - ISP 4PORT FOR SILABS C8051F MCU

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1300

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F342-GQ

Manufacturer:

SiliconL

Quantity:

1 428

Company:

Part Number:

C8051F342-GQ

Manufacturer:

SILICON

Quantity:

2 750

Company:

Part Number:

C8051F342-GQ

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Company:

Part Number:

C8051F342-GQ(R)

Manufacturer:

SILICO

Quantity:

1 730

Company:

Part Number:

C8051F342-GQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

C8051F342-GQR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

16.6. Function Addressing

The FADDR register holds the current USB0 function address. Software should write the host-assigned

7-bit function address to the FADDR register when received as part of a SET_ADDRESS command. A new

address written to FADDR will not take effect (USB0 will not respond to the new address) until the end of

the current transfer (typically following the status phase of the SET_ADDRESS command transfer). The

UPDATE bit (FADDR.7) is set to ‘1’ by hardware when software writes a new address to the FADDR regis-

ter. Hardware clears the UPDATE bit when the new address takes effect as described above.

16.7. Function Configuration and Control

The USB register POWER (SFR Definition 16.8) is used to configure and control USB0 at the device level

(enable/disable, Reset/Suspend/Resume handling, etc.).

USB Reset: The USBRST bit (POWER.3) is set to ‘1’ by hardware when Reset signaling is detected on

the bus. Upon this detection, the following occur:

Writing a ‘1’ to the USBRST bit will generate an asynchronous USB0 reset. All USB registers are reset to

their default values following this asynchronous reset.

Suspend Mode: With Suspend Detection enabled (SUSEN = ‘1’), USB0 will enter Suspend Mode when

Suspend signaling is detected on the bus. An interrupt will be generated if enabled (SUSINTE = ‘1’). The

Suspend Interrupt Service Routine (ISR) should perform application-specific configuration tasks such as

disabling appropriate peripherals and/or configuring clock sources for low power modes. See

Bit7:

Bits6–0: Function Address

Update

Bit7

R

1. The USB0 Address is reset (FADDR = 0x00).

2. Endpoint FIFOs are flushed.

3. Control/status registers are reset to 0x00 (E0CSR, EINCSRL, EINCSRH, EOUTCSRL,

4. USB register INDEX is reset to 0x00.

5. All USB interrupts (excluding the Suspend interrupt) are enabled and their corresponding flags

6. A USB Reset interrupt is generated if enabled.

Update: Function Address Update

Set to ‘1’ when software writes the FADDR register. USB0 clears this bit to ‘0’ when the new

address takes effect.

0: The last address written to FADDR is in effect.

1: The last address written to FADDR is not yet in effect.

Holds the 7-bit function address for USB0. This address should be written by software when

the SET_ADDRESS standard device request is received on Endpoint0. The new address

takes effect when the device request completes.

EOUTCSRH).

cleared.

USB Register Definition 16.7. FADDR: USB0 Function Address

R/W

Bit6

R/W

Bit5

R/W

Bit4

Function Address

C8051F340/1/2/3/4/5/6/7/8/9

Rev. 1.1

R/W

Bit3

R/W

Bit2

R/W

Bit1

R/W

Bit0

USB Address:

00000000

Reset Value

0x00

Section

185