MC908AZ60ACFUER Freescale Semiconductor, MC908AZ60ACFUER Datasheet - Page 186

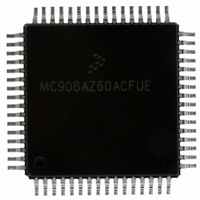

MC908AZ60ACFUER

Manufacturer Part Number

MC908AZ60ACFUER

Description

IC MCU 60K FLASH 8.4MHZ 64-QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908AZ60ACFUER.pdf

(414 pages)

Specifications of MC908AZ60ACFUER

Core Processor

HC08

Core Size

8-Bit

Speed

8.4MHz

Connectivity

CAN, SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

52

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 15x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-QFP

Processor Series

HC08AZ

Core

HC08

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SCI, SPI

Maximum Clock Frequency

8.4 MHz

Number Of Programmable I/os

52

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05CE, ZK-HC08AX-A, M68EM08AS/AZ60AE

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit, 15 Channel

Controller Family/series

HC08

No. Of I/o's

52

Eeprom Memory Size

1KB

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

MC908AZ60ACFUERTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

FREESCALE

Quantity:

5 560

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 186 of 414

- Download datasheet (5Mb)

Serial Communications Interface (SCI)

18.4.3.1 Character Length

The receiver can accommodate either 8-bit or 9-bit data. The state of the M bit in SCI control register 1

(SCC1) determines character length. When receiving 9-bit data, bit R8 in SCI control register 2 (SCC2)

is the ninth bit (bit 8). When receiving 8-bit data, bit R8 is a copy of the eighth bit (bit 7).

18.4.3.2 Character Reception

During an SCI reception, the receive shift register shifts characters in from the RxD pin. The SCI data

register (SCDR) is the read-only buffer between the internal data bus and the receive shift register.

After a complete character shifts into the receive shift register, the data portion of the character transfers

to the SCDR. The SCI receiver full bit, SCRF, in SCI status register 1 (SCS1) becomes set, indicating that

the received byte can be read. If the SCI receive interrupt enable bit, SCRIE, in SCC2 is also set, the

SCRF bit generates a receiver CPU interrupt request.

18.4.3.3 Data Sampling

The receiver samples the RxD pin at the RT clock rate. The RT clock is an internal signal with a frequency

16 times the baud rate. To adjust for baud rate mismatch, the RT clock is resynchronized at the following

times (see

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three

logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

186

•

•

After every start bit

After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit

samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and

RT10 samples returns a valid logic 0)

Figure

RT CLOCK

RT CLOCK

SAMPLES

CLOCK

RESET

STATE

MC68HC908AZ60A • MC68HC908AS60A • MC68HC908AS60E Data Sheet, Rev. 6

RxD

18-8):

RT

Figure 18-8. Receiver Data Sampling

QUALIFICATION

START BIT

VERIFICATION

START BIT

START BIT

SAMPLING

DATA

Freescale Semiconductor

LSB

Related parts for MC908AZ60ACFUER

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: