ATTINY461V-10MU Atmel, ATTINY461V-10MU Datasheet - Page 166

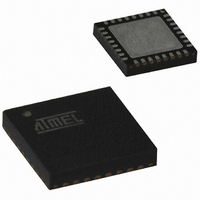

ATTINY461V-10MU

Manufacturer Part Number

ATTINY461V-10MU

Description

IC MCU AVR 4K FLASH 10MHZ 32-QFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY461V-10MU

Core Processor

AVR

Core Size

8-Bit

Speed

10MHz

Connectivity

USI

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

16

Program Memory Size

4KB (2K x 16)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 11x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-VQFN Exposed Pad, 32-HVQFN, 32-SQFN, 32-DHVQFN

Processor Series

ATTINY4x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

2-Wire, SPI, USI

Maximum Clock Frequency

10 MHz

Number Of Programmable I/os

16

Number Of Timers

2

Operating Supply Voltage

1.8 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 16 Channel

Package

32MLF EP

Device Core

AVR

Family Name

ATtiny

Maximum Speed

10 MHz

For Use With

ATSTK600 - DEV KIT FOR AVR/AVR32ATAVRBC100 - REF DESIGN KIT BATTERY CHARGER770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAG

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY461V-10MUR

Manufacturer:

Atmel

Quantity:

9 818

- Current page: 166 of 242

- Download datasheet (5Mb)

17.3

17.4

166

Performing a Page Write

Addressing the Flash During Self-Programming

ATtiny261/461/861

If the EEPROM is written in the middle of an SPM Page Load operation, all data loaded will be

lost.

To execute Page Write, set up the address in the Z-pointer, write “00000101” to SPMCSR and

execute SPM within four clock cycles after writing SPMCSR. The data in R1 and R0 is ignored.

The page address must be written to PCPAGE. Other bits in the Z-pointer must be written to

zero during this operation.

Note:

The Z-pointer is used to address the SPM commands.

Since the Flash is organized in pages (see

be treated as having two different sections. One section, consisting of the least significant bits, is

addressing the words within a page, while the most significant bits are addressing the pages.

This is shown in

addressed independently. Therefore it is of major importance that the software addresses the

same page in both the Page Erase and Page Write operation.

The LPM instruction uses the Z-pointer to store the address. Since this instruction addresses the

Flash byte-by-byte, also the LSB (bit Z0) of the Z-pointer is used.

Figure 17-1. Addressing the Flash During SPM

Note:

Bit

ZH (R31)

ZL (R30)

Z - REGISTER

The CPU is halted during the Page Write operation.

The different variables used in

PROGRAM MEMORY

BIT

15

Z15

Z7

7

PAGE

PROGRAM

COUNTER

15

Figure

PAGE ADDRESS

WITHIN THE FLASH

ZPCMSB

14

Z14

Z6

6

PCMSB

17-1. Note that the Page Erase and Page Write operations are

PCPAGE

13

Z13

Z5

5

Figure 17-1

ZPAGEMSB

12

Z12

Z4

4

PAGEMSB

Table 18-7 on page

PCWORD

are listed in

WORD ADDRESS

WITHIN A PAGE

11

Z11

Z3

3

1

0

0

INSTRUCTION WORD

Table 18-7 on page

10

Z10

Z2

2

PAGE

173), the Program Counter can

9

Z9

Z1

1

PCWORD[PAGEMSB:0]:

173.

00

01

02

PAGEEND

8

Z8

Z0

0

2588E–AVR–08/10

Related parts for ATTINY461V-10MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 4K 20MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 4K FLASH 20MHZ 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4K FLASH 15MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4KB FLASH 15MHZ 32-VQFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4KB FLASH 20MHZ 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 4K 20MHZ 32QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Microcontrollers (MCU) 4kB Flash 0.256kB EEPROM 16 I/O Pins

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 2K FLASH, 20SOIC

Manufacturer:

Atmel

Datasheet: