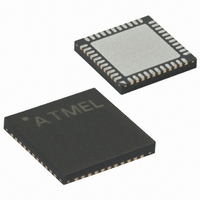

AT89LP6440-20MU Atmel, AT89LP6440-20MU Datasheet - Page 135

AT89LP6440-20MU

Manufacturer Part Number

AT89LP6440-20MU

Description

MCU 8051 64K FLASH ISP 44VQFN

Manufacturer

Atmel

Series

89LPr

Datasheet

1.AT89LP6440-20MU.pdf

(194 pages)

Specifications of AT89LP6440-20MU

Core Processor

8051

Core Size

8-Bit

Speed

20MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

38

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Eeprom Size

8K x 8

Ram Size

4.25K x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 3.6 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-VQFN Exposed Pad

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89LP6440-20MU

Manufacturer:

Atmel

Quantity:

987

- Current page: 135 of 194

- Download datasheet (6Mb)

20.1

3706A–MICRO–9/09

ADC Operation

The ADC converts an analog input voltage to a 10-bit signed digital value through successive

approximation. When DIFF (DADI.3) is zero, the ADC operates in single-ended mode and the

input voltage is the difference between the voltage at the input pin and AV

mode (DIFF = 1) the input voltage is the difference between the positive and negative input pins.

The minimum value represents zero difference and the maximum values represent a difference

of positive or negative V

The analog input channel is selected by writing to the ACS bits in DADI. Any of the eight Port 0

input pins can be selected as single-ended inputs to the ADC. Four pairs of Port 0 pins can be

selected as differential inputs. The ACON bit (DADI.7) must be set to one to connect the input

pins to the ADC. Prior to changing ACS, ACON must be cleared to zero. This ensures that

crosstalk between channels is limited. ACON must be set back to one after ACS is updated.

ACON and ACS should not be changed while a conversion is in progress. ADC input channels

must have their port pins configured for input-only mode.

The ADC is enabled by setting the ADCE bit in DADC. Some settling time is required for the ref-

erence circuits to stabilize after the ADC is enabled. The ADC does not consume power when

ADCE is cleared, so it is recommended to switch off the ADC before entering power saving

modes.

A timing diagram of an ADC conversion is shown in

ADC clock cycles to complete. The analog input is sampled during the third cycle of the conver-

sion and is held constant for the remainder of the conversion. At the end of the conversion, the

interrupt flag, ADIF, is set and the result is written to the data registers. An additional 1 ADC

clock cycle and up to 2 system clock cycles may be required to synchronize ADIF with the rest of

the system. The results in DADH/DADL remain valid until the next conversion completes. DADH

and DADL are read-only registers during ADC mode.

Figure 20-2. ADC Timing Diagram

The equivalent model for the analog input circuitry is illustrated in

applied to ADCn is subjected to the pin capacitance and input leakage of that pin, regardless of

whether that channel is selected as input to the ADC. When the channel is selected, the source

must drive the S/H capacitor through the series resistance (combined resistance in the input

path). To achieve 10-bit resolution the S/H capacitor must be charged to within 1/2 LSB of the

expected value within the 1 ADC clock period sample time. High impedance sources may

require a reduction in the ADC clock frequency to achieve full resolution.

Cycle Number

ADC Clock

GO/BSY

ADIF

DADH

DADL

1

2

Initialize Circuitry

REF

3

minus 1 LSB.

4

5

Sample & Hold

One Conversion

6

7

AT89LP6440 - Preliminary

8

Figure

9

10

Conversion

Complete

20-2. The conversion requires 13

11

Figure

12

13

20-3. An analog source

DD

MSB of Result

LSB of Result

/2. In differential

Next Conversion

1

2

Initialize

3

135

Related parts for AT89LP6440-20MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: