AT91SAM7X128B-CU-999 Atmel, AT91SAM7X128B-CU-999 Datasheet - Page 35

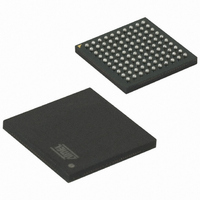

AT91SAM7X128B-CU-999

Manufacturer Part Number

AT91SAM7X128B-CU-999

Description

IC MCU ARM 128KB FLASH 100TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Datasheet

1.AT91SAM7X256B-CU.pdf

(45 pages)

Specifications of AT91SAM7X128B-CU-999

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

32 KB

Interface Type

CAN, I2S, JTAG, UASRT

Maximum Clock Frequency

55 MHz

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7X-EK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

10.6

10.7

10.8

6120FS–ATARM–17-Feb-09

Ethernet MAC

Serial Peripheral Interface

Two-wire Interface

• DMA Master on Receive and Transmit Channels

• Compatible with IEEE Standard 802.3

• 10 and 100 Mbit/s operation

• Full- and half-duplex operation

• Statistics Counter Registers

• MII/RMII interface to the physical layer

• Interrupt generation to signal receive and transmit completion

• 28-byte transmit FIFO and 28-byte receive FIFO

• Automatic pad and CRC generation on transmitted frames

• Automatic discard of frames received with errors

• Address checking logic supports up to four specific 48-bit addresses

• Support Promiscuous Mode where all valid received frames are copied to memory

• Hash matching of unicast and multicast destination addresses

• Physical layer management through MDIO interface

• Half-duplex flow control by forcing collisions on incoming frames

• Full-duplex flow control with recognition of incoming pause frames

• Support for 802.1Q VLAN tagging with recognition of incoming VLAN and priority tagged

• Multiple buffers per receive and transmit frame

• Jumbo frames up to 10240 bytes supported

• Supports communication with external serial devices

• Master or slave serial peripheral bus interface

• Master Mode only

• Compatibility with I

frames

– Four chip selects with external decoder allow communication with up to 15

– Serial memories, such as DataFlash

– Serial peripherals, such as ADCs, DACs, LCD Controllers, CAN Controllers and

– External co-processors

– 8- to 16-bit programmable data length per chip select

– Programmable phase and polarity per chip select

– Programmable transfer delays per chip select, between consecutive transfers and

– Programmable delay between consecutive transfers

– Selectable mode fault detection

– Maximum frequency at up to Master Clock

AT91SAM7X512/256/128 Preliminary Summary

peripherals

Sensors

between clock and data

2

C compatible devices (refer to the TWI section of the datasheet)

®

and 3-wire EEPROMs

35