SX1211I084TRT Semtech, SX1211I084TRT Datasheet - Page 40

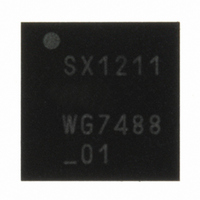

SX1211I084TRT

Manufacturer Part Number

SX1211I084TRT

Description

IC SNGL-CHIP TXRX 32-TQFN

Manufacturer

Semtech

Specifications of SX1211I084TRT

Frequency

860 ~ 960MHz

Data Rate - Maximum

200kbps

Modulation Or Protocol

FSK, OOK

Applications

AMR, ISM, Security and Access

Power - Output

12.5dBm

Sensitivity

-113dBm

Voltage - Supply

2.1 V ~ 3.6 V

Current - Receiving

3mA

Current - Transmitting

25mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Operating Temperature

-40°C ~ 85°C

Package / Case

32-TQFN

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Operating Temperature Classification

Industrial

Modulation Type

FSK/OOK

Package Type

TQFN EP

Operating Supply Voltage (min)

2.1V

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Memory Size

-

Lead Free Status / Rohs Status

Compliant

Other names

SX1211I084TRT

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SX1211I084TRT

Manufacturer:

HITTITE

Quantity:

560

Sync word recognition (also called Pattern recognition in previous products) is activated by setting

RXParam_Sync_on. The bit synchronizer must also be activated.

The block behaves like a shift register; it continuously compares the incoming data with its internally programmed

Sync word and asserts the Sync IRQ source on each occasion that a match is detected. This is illustrated in Figure

33.

During the comparison of the demodulated data, the first bit received is compared with bit 7 (MSB) of byte at

address 22 and the last bit received is compared with bit 0 (LSB) of the last byte whose address is determined by

the length of the Sync word.

When the programmed Sync word is detected the user can assume that this incoming packet is for the node and

can be processed accordingly.

The packet handler is the block used in Packet mode. Its functionality is fully described in section 5.5.

The control block configures and controls the full chip’s behavior according to the settings programmed in the

configuration registers.

Rev 7 – Sept 2

ADVANCED COMMUNICATIONS & SENSING

Size: Sync word size can be set to 8, 16, 24 or 32 bits via RXParam_Sync_size. In Packet mode this field is

also used for Sync word generation in Tx mode.

Error tolerance: The number of errors tolerated in the Sync word recognition can be set to 0, 1, 2 or 3 via

RXParam_Sync_tol.

Value: The Sync word value is configured in SYNCParam_Sync_value. In Packet mode this field is also used

for Sync word generation in Tx mode.

(NRZ)

DCLK

Rx DATA

SYNC

5.2.3. Sync Word Recognition

5.2.4. Packet Handler

5.2.5. Control

nd

, 2008

5.2.3.1. Overview

5.2.3.2. Configuration

Sync_value[x]

Bit N-x =

Figure 33: Sync Word Recognition

Sync_value[1]

Bit N-1 =

Page 40 of 92

Sync_value[0]

Bit N =

www.semtech.com

SX1211