AGL400V5-FGG484 Actel, AGL400V5-FGG484 Datasheet - Page 95

AGL400V5-FGG484

Manufacturer Part Number

AGL400V5-FGG484

Description

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer

Actel

Datasheet

1.AGL030V2-CSG81.pdf

(236 pages)

Specifications of AGL400V5-FGG484

Processor Series

AGL400

Core

IP Core

Number Of Logic Blocks

12

Maximum Operating Frequency

250 MHz

Number Of Programmable I/os

194

Data Ram Size

54 Kbit

Supply Voltage (max)

1.5 V

Supply Current

27 uA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Development Tools By Supplier

AGL-Icicle-Kit, AGL-Dev-Kit-SCS, Silicon-Explorer II, Silicon-Sculptor 3, SI-EX-TCA, FlashPro 4, FlashPro 3, FlashPro Lite

Mounting Style

SMD/SMT

Supply Voltage (min)

1.425 V

Number Of Gates

400 K

Package / Case

FPBGA-484

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AGL400V5-FGG484

Manufacturer:

Actel

Quantity:

135

Company:

Part Number:

AGL400V5-FGG484

Manufacturer:

Microsemi SoC

Quantity:

10 000

Company:

Part Number:

AGL400V5-FGG484I

Manufacturer:

Microsemi SoC

Quantity:

10 000

- Current page: 95 of 236

- Download datasheet (8Mb)

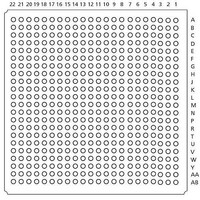

Figure 2-13 • LVDS Circuit Diagram and Board-Level Implementation

OUTBUF_LVDS

Differential I/O Characteristics

Physical Implementation

Configuration of the I/O modules as a differential pair is handled by Actel Designer software when the

user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output

Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no

support for bidirectional I/Os or tristates with the LVPECL standards.

LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It

requires that one data bit be carried through two signal lines, so two pins are needed. It also requires

external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in

building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three

board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver

resistors are different from those used in the LVPECL implementation because the output standard

specifications are different.

Along with LVDS I/O, IGLOO also supports Bus LVDS structure and Multipoint LVDS (M-LVDS)

configuration (up to 40 nodes).

FPGA

P

N

Bourns Part Number: CAT16-LV4F12

165 Ω

165 Ω

140 Ω

R ev i si o n 1 8

Z

Z

0

0

= 50 Ω

= 50 Ω

100 Ω

N

P

IGLOO Low Power Flash FPGAs

FPGA

+

–

INBUF_LVDS

Figure

2-13. The

2- 81

Related parts for AGL400V5-FGG484

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

PBGA 196/FPGA, 9216 CLBS, 400000 GATES

Manufacturer:

Actel

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Silicon Sculptor Programming Mod

Manufacturer:

Actel

Part Number:

Description:

MCU, MPU & DSP Development Tools InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators PQ160 Module

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel