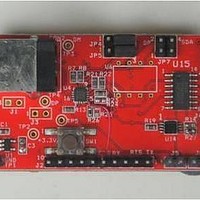

XR21V1410IL-0C-EB Exar Corporation, XR21V1410IL-0C-EB Datasheet

XR21V1410IL-0C-EB

Specifications of XR21V1410IL-0C-EB

Related parts for XR21V1410IL-0C-EB

XR21V1410IL-0C-EB Summary of contents

Page 1

APRIL 2011 GENERAL DESCRIPTION The XR21V1410 (V1410 enhanced Universal Asynchronous Receiver and Transmitter (UART) with a USB interface. The USB interface is fully compliant to Full Speed USB 2.0 specification that supports 12 Mbps USB data transfer rate. ...

Page 2

... VCC GND IGURE IN UT SSIGNMENT GND USBD- USBD+ ORDERING INFORMATION P N ART UMBER XR21V1410IL16-F 16-pin QFN XR21V1410IL16TR-F 16-pin QFN Tape and Reel Green / RoHS OTE 128-byte TX FIFO Fractional BRG 384-byte RX FIFO Internal Status and GPIOs/ Control Modem IO Registers UART GPIO0/RI#/RWK# ...

Page 3

REV. 1.2.0 PIN DESCRIPTIONS Pin Description 16-QFN N AME UART Signals GPIO0/RI#/RWK# 7 GPIO1/CD# 6 GPIO2/DSR# 5 GPIO3/DTR# 4 GPIO4/CTS# 3 GPIO5/RTS# T YPE I UART Channel A Receive Data or IR ...

Page 4

XR21V1410 1-CH FULL-SPEED USB UART Pin Description 16-QFN N AME USB Interface Signals USBD+ 15 USBD Interface Signals SDA 11 I/O OD SCL 12 Miscellaneous Signals 2 LOWPOWER 16 VCC 1, 13 GND ...

Page 5

REV. 1.2.0 1.0 FUNCTIONAL DESCRIPTIONS 1.1 USB interface The USB interface of the V1410 is compliant with the USB 2.0 Full-Speed Specifications. The USB configuration model presented by the V1410 to the device driver is compatible to the Abstract Control ...

Page 6

XR21V1410 1-CH FULL-SPEED USB UART 2 1 Interface 2 The I C interface provides connectivity to an external I the V1410 for configuration. The SDA and SCL are used to specify whether Remote Wakeup and/or Bus Powered configurations ...

Page 7

REV. 1.2.0 Bit 6 is Self-powered mode - set to ’0’ for bus-powered, set to ’1’ for self-powered Bit 5 is Remote Wakeup support - set to ’0’ for no support, set to ’1’ for remote wakeup support Bit 4:0 ...

Page 8

XR21V1410 1-CH FULL-SPEED USB UART bit m ode 1st byte 2nd byte 1st byte ...

Page 9

REV. 1.2 RTS CTS F IGURE UTO AND LOW Local UART UARTA Receiver FIFO Trigger Reached Auto RTS Trigger Level Transmitter Auto CTS Monitor Assert RTS# to Begin Transmission 1 RTSA# 2 CTSB# 3 TXB Data Starts ...

Page 10

XR21V1410 1-CH FULL-SPEED USB UART 1.5.7.1 Receiver If an address match occurs in either flow control mode the address byte will not be loaded into the RX FIFO, but all subsequent data bytes will be loaded into ...

Page 11

REV. 1.2.0 2.0 USB CONTROL COMMANDS The following table shows all of the USB Control Commands that are supported by the V1410. Commands included are standard USB commands, CDC-ACM commands and custom Exar commands. T ABLE R EQUEST N AME ...

Page 12

XR21V1410 1-CH FULL-SPEED USB UART T ABLE R EQUEST N AME T YPE CDC_ACM_IF 0x21 SEND_BREAK XR_SET_REG 0x40 XR_GETN_REG 0xC0 2.1 UART Block Numbers The table below lists the block numbers for accessing each of the UART channels and the ...

Page 13

REV. 1.2.0 3.0 REGISTER SET DESCRIPTION The internal register set of the V1410 consists of 3 different blocks of registers: the UART Manager, UART registers and UART miscellaneous registers. The UART Manager controls the TX and RX enables and FIFOs ...

Page 14

XR21V1410 1-CH FULL-SPEED USB UART 3.2 UART Register Map DDRESS EGISTER AME 0X00 Reserved 0X01 Reserved 0X02 Reserved 0X03 UART_ENABLE 0X04 CLOCK_DIVISOR0 0x05 CLOCK_DIVISOR1 0x06 CLOCK_DIVISOR2 0x07 TX_CLOCK_MASK0 0x08 TX_CLOCK_MASK1 0x09 RX_CLOCK_MASK0 0x0A RX_CLOCK_MASK1 0x0B CHARACTER_FORMAT 0x0C ...

Page 15

REV. 1.2.0 3.3 UART Register Descriptions 3.3.1 UART_ENABLE Register Description (Read/Write) This register enables the UART TX and RX. For proper functionality, the UART TX and RX must be enabled in the following order: FIFO_ENABLE = 0x1 UART_ENABLE = 0x3 ...

Page 16

XR21V1410 1-CH FULL-SPEED USB UART ABLE LOCK IVISOR AND AUD ATE BPS LOCK 1200 2400 4800 9600 19200 38400 57600 115200 230400 460800 500000 576000 921600 1000000 1152000 1500000 2000000 2500000 ...

Page 17

REV. 1.2 NDEX ECIMAL ...

Page 18

XR21V1410 1-CH FULL-SPEED USB UART 3.3.5 CHARACTER_FORMAT Register Description (Read/Write) This register controls the character format such as the word length ( 9), parity (odd, even, forced ’0’, or forced ’1’) and number of stop bits (1 or ...

Page 19

REV. 1.2.0 FLOW_CONTROL[2:0]: Flow control mode select T ABLE ODE ...

Page 20

XR21V1410 1-CH FULL-SPEED USB UART 3.3.9 ERROR_STATUS Register Description - Read-only This register reports any errors that may have occurred on the line such as break, framing, parity and overrun. ERROR_STATUS[2:0]: Reserved These bits are reserved. Any values read from ...

Page 21

REV. 1.2.0 ERROR_STATUS[4]: Framing Error Logic framing error Logic framing error has been detected (clears after read). A framing error occurs when a stop bit is not present when it is expected. ERROR_STATUS[5]: Parity ...

Page 22

XR21V1410 1-CH FULL-SPEED USB UART GPIO_MODE[3]: Transceiver Enable Polarity Logic 0 = GPIO5 Low for TX Logic 1 = GPIO5 High for TX GPIO_MODE[7:4]: Reserved These register bits are reserved. When writing to these bits, the value should be ’0’. ...

Page 23

REV. 1.2.0 3.4.1 WIDE_MODE Register Description (Read/Write) This register enables the Wide mode functionality for the UART. WIDE_MODE[0]: Enable wide mode Logic 0 = Normal ( bit data) mode Logic 1 = Wide mode - See “Section ...

Page 24

XR21V1410 1-CH FULL-SPEED USB UART Logic 0 = Disable GPIO4 status in custom interrupt packet. Logic 1 = Enable GPIO4 status in custom interrupt packet. CUSTOM_INT_PACKET[6]: GPIO5 Logic 0 = Disable GPIO5 status in custom interrupt packet. Logic 1 = ...

Page 25

REV. 1.2.0 If the Exar vendor specific packet mapping is enabled then the data field also includes status for all of the UART / GPIO pins as follows ABLE ATA IELD ...

Page 26

XR21V1410 1-CH FULL-SPEED USB UART 4.0 ELECTRICAL CHARACTERISTICS DC ELECTRICAL CHARACTERISTICS - POWER CONSUMPTION -40 NLESS OTHERWISE NOTED S P YMBOL ARAMETER I Power Supply Current CC I Suspend mode Current Susp DC ELECTRICAL CHARACTERISTICS - ...

Page 27

REV. 1.2.0 PACKAGE DIMENSIONS (16 PIN QFN - 0.9 Note: The control dimension is the millimeter column SYMBOL INCHES MILLIMETERS MIN MAX MIN 0.031 0.035 ...

Page 28

... Updated ordering information, SDA/SCL pin types, modified GPIO0 pin name and added LOOPBACK_CTL register and description. EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement ...