AD7716BPZ Analog Devices Inc, AD7716BPZ Datasheet - Page 13

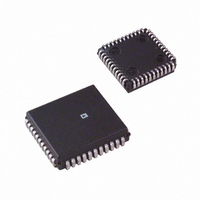

AD7716BPZ

Manufacturer Part Number

AD7716BPZ

Description

4-CHNL S-D ADC

Manufacturer

Analog Devices Inc

Datasheet

1.AD7716BP-REEL.pdf

(16 pages)

Specifications of AD7716BPZ

Number Of Bits

22

Sampling Rate (per Second)

2.23k

Data Interface

Serial

Number Of Converters

4

Power Dissipation (max)

50mW

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

44-PLCC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

EVAL-AD7716EBZ - BOARD EVAL FOR AD7716

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AD7716BPZ

Manufacturer:

ST

Quantity:

2 100

Company:

Part Number:

AD7716BPZ

Manufacturer:

Analog Devices Inc

Quantity:

10 000

RESET

The AD7716 has a hardware reset which can be used to synchro-

nize many devices. When the RESET pin goes low after being

high for at least four CLKIN cycles, the modulator sampling

points and digital filter starting points are all synchronized. This

synchronizes all devices which receive the RESET pulse and

gives simultaneous sampling of all channels. It does not affect

the control register but restarts the interface. Also, it is necessary

to wait the requisite settling time after applying Reset to get valid

data from the device.

CASCADING DEVICES

The AD7716 provides a facility for connecting multiple devices

in series. The CASCIN and CASCOUT pins allow this. Con-

necting CASCOUT to CASCIN of the succeeding device means

that the SDATA output of the second device will be disabled un-

til the output register of the first device is empty.

In the case of the first device in the system, it is possible to drive

CASCIN from CASCOUT of the last device or, alternatively,

invert DRDY to drive it. If CASCIN is driven by CASCOUT,

then a reset must be applied after every write to the control

register. This also applies in single device systems that use

CASCOUT to drive CASCIN

DATA OUTPUT INTERFACE MODES

When the control register has been programmed, the device be-

gins conversion. There is an initial delay to allow the digital fil-

ters to settle. As already stated, these filters are Sinc

filter output update rate is directly related to the programmed

cutoff frequency. The ratio between these is 3.81. So, for a filter

cutoff frequency of 584 Hz, the output update is 2.22 kHz. The

falling edge of the DRDY output indicates that the output shift

register has been updated. There are two interface modes. One

is the master mode, where the AD7716 is the master in the sys-

tem and the processor to which it is communicating is the slave.

The other mode is the slave mode, where the AD7716 is the

slave and the processor is the system master. In both of these

modes the data output stream contains 4

ing to the four input channels. The output data format is given

in Table V. The conversion result DB21–DB0 occupies location

DB31–DB10 of the output register. DB21 is the MSB and is

transmitted first as shown in the timing diagrams. The channel

address is given by CA0 and CA1 which occupy DB9 and DB8

of the output register. The channel address format is given in

Table VI.

DB31 . . . DB10

DB21 . . . DB0

Conversion Result

Channel

A

A

A

A

REV. A

IN

IN

IN

IN

1

2

3

4

Table VI. Channel Address Format

DB9

CA0

Channel Address

CA1 (DB8)

0

0

1

1

DB8

CA1

32 bits, correspond-

Table V. Output Data Word Format

A0

DB7

Device Address

CA0 (DB9)

0

1

0

1

3

, and so the

DB6 DB5

A1

A2

–13–

Master Mode Interface

The device may be placed in the Master Mode by tying the

MODE pin low. In this mode, data is clocked out of the

AD7716 by an internally generated serial clock and frame syn-

chronization pulse. Two signals initiate the transfer. These are

the input CASCIN and the internally generated DRDY signal.

When a high level is detected on CASCIN, the device checks

the state of DRDY. Note, that on initial power-up or after a re-

set has been applied, the CASCIN input is not necessary on de-

vice 000 for the first data transfer but is required thereafter. If

DRDY is low, then the 3-state output, RFS goes high on the

next rising edge of CLKIN and stays high for one CLKIN cycle

before going low again. The 3-state SCLK output is also acti-

vated on the same rising edge. As RFS goes low, DB31 is

clocked out on the rising edge of SCLK and is valid on the fall-

ing edge of SCLK. Data is transmitted in 8-bit bytes. For each

A

A

the CASCOUT output goes high for one master clock cycle.

DRDY also goes high at this point. Successive devices can be

networked together by tying the CASCOUT of one device to

the CASCIN on the next one.

Note that on device 0 (A2, A1, A0 tied low), the CASCIN input

should be driven by the inverse of the DRDY output. This is

shown in the interface diagram of Figure 8.

The Master Mode interface is very suitable for loading data into

a serial-to-parallel shift register or for DSPs which can accept a

continuous stream of 8-bit bytes.

Slave Mode Interface

The device may be placed in the slave interface mode by tying

the MODE pin high. In this mode, the master processor con-

trols the transfer of data from the signal processing block. It

starts the transfer by sending a frame synchronizations pulse and

serial clock to the AD7716. This could be in response to an in-

terrupt generated by the DRDY output on the AD7716. If the

device has detected a high level on CASCIN or is device 000 on

its first transfer, it starts to send out data on the next rising edge

of SCLK. This data is then valid on the falling edge of SCLK.

When all the data bits have been clocked out, the CASCOUT

pin goes high for one CLKIN cycle and DRDY also goes high.

The slave mode interface is suited to both microcomputers like

the 8051 and 68HC11 and also DSPs like the TMS320C25,

ADSP-2101 family and the DSP56000 family.

IN

IN

, there are 4, 8-bit bytes and 4 RFS pulses. When DB0 of

4 has been clocked out, SCLK goes back into 3-state and

DB4

D

Pace Detect

IN

1

DB3

OVFL

Overflow

DB2

X

Indeterminate

AD7716

DB1

X

DB0

X