MT9V032C12STC Aptina LLC, MT9V032C12STC Datasheet - Page 12

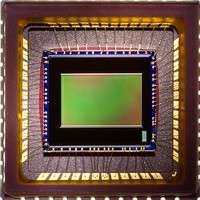

MT9V032C12STC

Manufacturer Part Number

MT9V032C12STC

Description

SENSOR IMAGE VGA COLOR 48LCC

Manufacturer

Aptina LLC

Series

DigitalClarity®, Micron®r

Type

CMOS Imagingr

Datasheet

1.MT9V032C12STM.pdf

(13 pages)

Specifications of MT9V032C12STC

Pixel Size

6µm x 6µm

Active Pixel Array

752H x 480V

Frames Per Second

60

Voltage - Supply

3.3V

Package / Case

48-CLCC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

557-1237

MT9V032C12STC ES

Q3986409

MT9V032C12STC ES

Q3986409

Broadcast and Individual Writes for Stereoscopic Topology

Figure 8:

PDF: 09005aef824c9998/Source: 09005aef824c999c

MT9V032_LDS_2.fm - Rev. B 3/07 EN

Two-Wire Serial Interface Configuration in Stereoscopic Mode

In stereoscopic mode, the two sensors are required to run in lockstep. This implies that

control logic in each sensor is in exactly the same state as its pair on every clock. To

ensure this, all inputs that affect control logic must be identical and arrive at the same

time at each sensor.

These inputs include:

• system clock

• system reset

• two-wire serial interface clk - SCL

• two-wire serial interface data - SDA

The setup in Figure 8 shows how the two sensors can maintain lockstep when their

configuration registers are written through the two-wire serial interface. A WRITE to

configuration registers would either be broadcast (simultaneous WRITES to both

sensors) or individual (WRITE to just one sensor at a time). READs from configuration

registers would be individual (READs from just one sensor at a time).

One of the two serial interface slave address bits of the sensor is hardwired. The other is

controlled by the host. This allows the host to perform either a broadcast or a one-to-

one access.

Broadcast WRITES are performed by setting the same S_CTRL_ADR input bit for both

slave and master sensor. Individual WRITES are performed by setting opposite

S_CTRL_ADR input bit for both slave and master sensor. Similarly, individual READs are

performed by setting opposite S_CTRL_ADR input bit for both slave and master sensor.

26.6 MHz

Osc.

All system clock lengths (L) must be equal.

SCL and SDA lengths to each sensor (from the host) must also be equal.

HOST

L

CLK

MT9V032: 1/3-Inch Wide-VGA Digital Image Sensor

SCL

SDA

L

S_CTRL_ADR[0]

SCL

12

SENSOR

SLAVE

Host launches SCL and SDA on positive

edge of SYSCLK.

SDA

L

Micron Technology, Inc., reserves the right to change products or specifications without notice.

CLK

Appendix A – Serial Configurations

S_CTRL_ADR[0]

SCL

MASTER

SENSOR

©2006 Micron Technology, Inc. All rights reserved.

SDA

CLK

Preliminary

‡