KAC-9618 Eastman Kodak Company, KAC-9618 Datasheet - Page 25

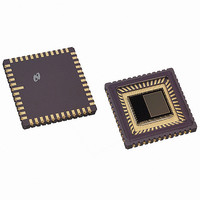

KAC-9618

Manufacturer Part Number

KAC-9618

Description

IC SENSOR IMAGE VGA MONO 48-CLCC

Manufacturer

Eastman Kodak Company

Type

CMOS Imagingr

Datasheet

1.KAC-9618.pdf

(43 pages)

Specifications of KAC-9618

Pixel Size

7.5µm x 7.5µm

Active Pixel Array

648H x 488V

Frames Per Second

30

Voltage - Supply

3.3V

Package / Case

48-CLCC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

LM9618IEA

LM9618IEA

LM9618IEA

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

KAC-9618

Manufacturer:

IXYS

Quantity:

2 100

IMAGE SENSOR SOLUTIONS

Functional Description

11.6

The sensor’s digital video port’s synchronisation signals can be

programmed to operate in slave mode. In slave mode the inte-

grated timing and control block will only start frame and row pro-

cessing upon the receipt of triggers from an external source.

Only two synchronization signals are used in slave mode as fol-

lows:

Figure 48 shows the KAC-9618’s digital video port in slave

mode connected to a digital video processor master DVP.

www.kodak.com/go/imagers 585-722-4385

hsync

vsync

internal row

Synchronisation Signals in Slave Mode

counter

hsync

mclk

vsync

count

mclk

KAC-9618

Figure 48. KAC-9618 in slave mode

is the row trigger input signal.

is the frame trigger input signal.

d[11:0]

hsync

vsync

d[11:0]

hsync

count

mclk

mclk

mclk

pclk

Figure 49. hsync slave mode timing diagram for centred display window of 642 pixels

776

line 502

Figure 50. vsync slave mode timing diagram for scan window of 504 rows.

777

96 clock cycles

778

No more than

776

779

777

0

(continued)

778

din[11:0]

RowTrig

FrameTrig

MasterClock

1

779

DVP

2

780 clock cycles per line

0

3

1

line502

2

...

3

774

...

780 clock cycles per line

775

25

776

134 135 136 136 137

pixel 11

11.7

The row trigger input pin, hsync, is used to trigger the process-

ing of a given row. It must be activated for at least two “mclk”

cycle. The first pixel data will appear at d[11:0] “X

after the assertion of the row trigger, were X

Where:

The polarity of the active level of the row trigger is programma-

ble. By default it is active high.

11.8

The frame trigger input pin, vsync, is used to reset the row

address counter and prepare the array for row processing. It

must be activated for at least one “mclk” cycle and no more than

96 mclk cycles after the activation of hsync as illustrated in Fig-

ure 50.

The polarity of the active level of the row trigger is programma-

ble. By default it is active high.

777

778

DW

pixel 12

779

Row Trigger Input Pin (hsync)

Frame Trigger Input Pin (vsync)

StAd

0

642 valid pixels

1

is the value of the display window column start

address.

...

X

mclk

...

774

line503

= 124 + DW

775

774

776

775

777

pixel 652

776

778

Email:imagers@kodak.com

777

StAd

779

778

0

779

mclk

1

0

is given by:

line 0

1

mclk

“periods