DS1743WP-120+ Maxim Integrated Products, DS1743WP-120+ Datasheet - Page 4

DS1743WP-120+

Manufacturer Part Number

DS1743WP-120+

Description

IC RTC RAM Y2K 3.3V 120NS 34-PCM

Manufacturer

Maxim Integrated Products

Type

Clock/Calendar/NVSRAM/Y2Kr

Datasheet

1.DS1743W-120.pdf

(16 pages)

Specifications of DS1743WP-120+

Memory Size

64K (8K x 8)

Time Format

HH:MM:SS (24 hr)

Date Format

YY-MM-DD-dd

Interface

Parallel

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

34-PowerCap™ Module

Function

Clock/Calendar/NV Timekeeping RAM

Rtc Memory Size

8192 Byte

Supply Voltage (max)

3.63 V

Supply Voltage (min)

2.97 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

Through Hole

Rtc Bus Interface

Parallel

Supply Current

15 mA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

DS1743/DS1743P Y2K-Compliant, Nonvolatile Timekeeping RAMs

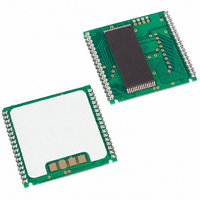

PACKAGES

The DS1743 is available in two packages: the 28-pin DIP and the 34-pin PowerCap module. The 28-pin

DIP-style module integrates the crystal, lithium energy source, and silicon all in one package. The 34-pin

PowerCap Module Board is designed with contacts for connection to a separate PowerCap (DS9034PCX)

that contains the crystal and battery. This design allows the PowerCap to be mounted on top of the

DS1743P after the completion of the surface-mount process. Mounting the PowerCap after the surface-

mount process prevents damage to the crystal and battery due to the high temperatures required for solder

reflow. The PowerCap is keyed to prevent reverse insertion. The PowerCap Module Board and PowerCap

are ordered separately and shipped in separate containers. The part number for the PowerCap is

DS9034PCX.

TIME AND DATE OPERATION

The time and date information is obtained by reading the appropriate register bytes. Table 2 shows the

RTC registers. The time and date are set or initialized by writing the appropriate register bytes. The

contents of the time and date registers are in the BCD format. The day-of-week register increments at

midnight. Values that correspond to the day of week are user-defined, but must be sequential (i.e., if 1

equals Sunday, then 2 equals Monday and so on). Illogical time and date entries result in undefined

operation.

CLOCK OPERATIONS-READING THE CLOCK

While the double-buffered register structure reduces the chance of reading incorrect data, internal updates

to the DS1743 clock registers should be halted before clock data is read to prevent reading of data in

transition. However, halting the internal clock register updating process does not affect clock accuracy.

Updating is halted when a 1 is written into the read bit, bit 6 of the century register (see Table 2). As long

as a 1 remains in that position, updating is halted. After a halt is issued, the registers reflect the count that

is day, date, and time that was current at the moment the halt command was issued. However, the internal

clock registers of the double-buffered system continue to update so that the clock accuracy is not affected

by the access of data. All the DS1743 registers are updated simultaneously after the internal clock register

updating process has been re-enabled. Updating is within a second after the read bit is written to 0.

The READ bit must be a zero for a minimum of 500s to ensure the external registers are updated.

4 of 16