EPM7256EGI192-20 Altera, EPM7256EGI192-20 Datasheet - Page 19

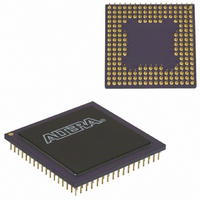

EPM7256EGI192-20

Manufacturer Part Number

EPM7256EGI192-20

Description

IC MAX 7000 CPLD 256 192-PGA

Manufacturer

Altera

Series

MAX® 7000r

Datasheet

1.EPM7064STC44-10.pdf

(66 pages)

Specifications of EPM7256EGI192-20

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

20.0ns

Voltage Supply - Internal

4.5 V ~ 5.5 V

Number Of Logic Elements/blocks

16

Number Of Macrocells

256

Number Of Gates

5000

Number Of I /o

164

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

192-PGA

Voltage

5V

Memory Type

EEPROM

Number Of Logic Elements/cells

16

Family Name

MAX 7000

# Macrocells

256

Number Of Usable Gates

5000

Frequency (max)

83.33MHz

Propagation Delay Time

20ns

Number Of Logic Blocks/elements

16

# I/os (max)

164

Operating Supply Voltage (typ)

5V

In System Programmable

Yes

Operating Supply Voltage (min)

4.5V

Operating Supply Voltage (max)

5.5V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Through Hole

Pin Count

192

Package Type

CPGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2356

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EPM7256EGI192-20

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Altera Corporation

Table 6. MAX 7000S t

Table 7. MAX 7000S In-System Programming Times for Different Test Clock Frequencies

Table 8. MAX 7000S Stand-Alone Verification Times for Different Test Clock Frequencies

EPM7032S

EPM7064S

EPM7128S

EPM7160S

EPM7192S

EPM7256S

EPM7032S

EPM7064S

EPM7128S

EPM7160S

EPM7192S

EPM7256S

Device

Device

EPM7032S

EPM7064S

EPM7128S

EPM7160S

EPM7192S

EPM7256S

Device

10 MHz

10 MHz

4.06

4.55

5.19

5.45

5.83

6.59

0.05

0.06

0.08

0.09

0.11

0.13

PULSE

5 MHz

5 MHz

The programming times described in

with the worst-case method using the enhanced ISP algorithm.

Tables 7

verification times for several common test clock frequencies.

& Cycle

4.09

4.60

5.27

5.55

5.95

6.75

0.07

0.09

0.14

0.16

0.18

0.24

t

PPULSE

4.02

4.50

5.11

5.35

5.71

6.43

TCK

and

2 MHz

2 MHz

4.19

4.76

5.52

5.85

6.30

7.23

0.13

0.18

0.29

0.35

0.41

0.54

(s)

Values

Programming

8

show the in-system programming and stand alone

MAX 7000 Programmable Logic Device Family Data Sheet

1 MHz

1 MHz

4.36

5.01

5.94

6.35

6.90

8.03

0.23

0.34

0.56

0.67

0.79

1.06

Cycle

1,001,000

1,192,000

1,603,000

342,000

504,000

832,000

f

f

TCK

TCK

PTCK

500 kHz

500 kHz

4.71

5.51

6.77

7.35

8.09

9.64

0.43

0.64

1.09

1.31

1.56

2.08

Tables 6

200 kHz

200 kHz

10.35

11.67

14.45

1.03

1.57

2.67

3.23

3.85

5.15

5.73

7.02

9.27

t

VPULSE

Stand-Alone Verification

0.03

0.03

0.03

0.03

0.03

0.03

through

(s)

100 kHz

100 kHz

13.43

15.36

17.63

22.46

10.27

7.44

9.54

2.03

3.11

5.31

6.43

7.67

8

are associated

50 kHz

50 kHz

10.86

14.58

21.75

25.37

29.55

38.49

10.59

12.83

15.31

20.51

1,024,000

Cycle

4.03

6.19

200,000

308,000

528,000

640,000

764,000

VTCK

Units

Units

s

s

s

s

s

s

s

s

s

s

s

s

19