EP2C70F896I8 Altera, EP2C70F896I8 Datasheet - Page 35

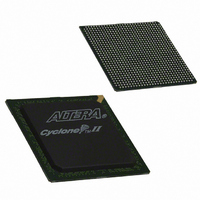

EP2C70F896I8

Manufacturer Part Number

EP2C70F896I8

Description

IC CYCLONE II FPGA 70K 896-FBGA

Manufacturer

Altera

Series

Cyclone® IIr

Datasheet

1.EP2C5T144C8N.pdf

(168 pages)

Specifications of EP2C70F896I8

Number Of Logic Elements/cells

68416

Number Of Labs/clbs

4276

Total Ram Bits

1152000

Number Of I /o

622

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

896-FBGA

For Use With

P0304 - DE2-70 CALL FOR ACADEMIC PRICING544-1703 - VIDEO KIT W/CYCLONE II EP2C70N544-1699 - DSP KIT W/CYCLONE II EPS2C70N

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-2146

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP2C70F896I8

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EP2C70F896I8N

Manufacturer:

ALTERA21

Quantity:

196

Part Number:

EP2C70F896I8N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Figure 2–14. Global Clock Network Multiplexers

Altera Corporation

February 2007

Global Clock

Network

Clock [15 or 7..0]

Global Clock Network Distribution

Cyclone II devices contains 16 global clock networks. The device uses

multiplexers with these clocks to form six-bit buses to drive column IOE

clocks, LAB row clocks, or row IOE clocks (see

multiplexer at the LAB level selects two of the six LAB row clocks to feed

the LE registers within the LAB.

LAB row clocks can feed LEs, M4K memory blocks, and embedded

multipliers. The LAB row clocks also extend to the row I/O clock regions.

IOE clocks are associated with row or column block regions. Only six

global clock resources feed to these row and column regions.

shows the I/O clock regions.

Cyclone II Device Handbook, Volume 1

Column I/O Region

IO_CLK [5..0]

LAB Row Clock

LABCLK[5..0]

Row I/O Region

IO_CLK [5..0]

Figure

Cyclone II Architecture

2–14). Another

Figure 2–15

2–23