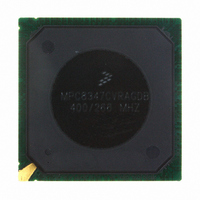

MPC8347CVRAGDB Freescale Semiconductor, MPC8347CVRAGDB Datasheet - Page 33

MPC8347CVRAGDB

Manufacturer Part Number

MPC8347CVRAGDB

Description

IC MPU POWERQUICC II 620-PBGA

Manufacturer

Freescale Semiconductor

Series

PowerQUICC II PROr

Specifications of MPC8347CVRAGDB

Processor Type

MPC83xx PowerQUICC II Pro 32-Bit

Speed

400MHz

Voltage

1.2V

Mounting Type

Surface Mount

Package / Case

620-PBGA

Core Size

32 Bit

Program Memory Size

64KB

Cpu Speed

400MHz

Embedded Interface Type

I2C, SPI, USB, UART

Digital Ic Case Style

BGA

No. Of Pins

672

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC8347CVRAGDB

Manufacturer:

FREESCA

Quantity:

13

Company:

Part Number:

MPC8347CVRAGDB

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Figure 16

Freescale Semiconductor

At recommended operating conditions with LV

MDC fall time

Notes:

1. The symbols for timing specifications follow the pattern of t

2. This parameter is dependent on the csb_clk speed (that is, for a csb_clk of 267 MHz, the maximum frequency is 8.3 MHz

3. This parameter is dependent on the csb_clk speed (that is, for a csb_clk of 267 MHz, the delay is 70 ns and for a csb_clk of

and t

timing (MD) for the time t

t

relative to the t

is used with the appropriate letter: R (rise) or F (fall).

and the minimum frequency is 1.2 MHz; for a csb_clk of 375 MHz, the maximum frequency is 11.7 MHz and the minimum

frequency is 1.7 MHz).

333 MHz, the delay is 58 ns).

MDDVKH

(first two letters of functional block)(reference)(state)(signal)(state)

symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V)

Parameter/Condition

shows the MII management AC timing diagram.

MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications, Rev. 11

MDC

(Output)

(Input)

MDIO

MDIO

clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention

MDC

Table 34. MII Management AC Timing Specifications (continued)

MDC

Figure 16. MII Management Interface Timing Diagram

from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also,

t

MDCH

DD

t

is 3.3 V ± 10% or 2.5 V ± 5%.

MDDVKH

t

MDC

t

MDKHDX

Symbol

t

MDHF

1

for outputs. For example, t

(first two letters of functional block)(signal)(state)(reference)(state)

t

MDCF

Min

—

t

MDDXKH

t

MDCR

Ethernet: Three-Speed Ethernet, MII Management

Typ

—

MDKHDX

Max

symbolizes management data

10

Unit

ns

for inputs

Notes

—

33