THC63LVDM63A THine Electronics, THC63LVDM63A Datasheet

THC63LVDM63A

Available stocks

Related parts for THC63LVDM63A

THC63LVDM63A Summary of contents

Page 1

... CMOS/TTL data into LVDS(Low Voltage Differential Signaling) data stream. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. The THC63LVDM63A can be programmed for rising edge or falling edge clocks through a dedicated pin. The THC63LVDF64A receiver convert the LVDS data streams back into 21 bits of CMOS/TTL data with falling edge clock ...

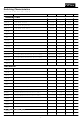

Page 2

... PIN OUT TRANSMITTER DEVICE THC63LVDM63A 1 TA4 2 VCC 3 TA5 4 TA6 5 GND 6 TB0 7 TB1 8 VCC 9 TB2 10 TB3 11 GND 12 TB4 13 TB5 14 R/F 15 TB6 16 TC0 17 GND 18 TC1 19 TC2 20 TC3 21 VCC 22 TC4 23 TC5 24 GND PACKAGE 48 Lead Molded Thin Shrink Small Outline Package, JEDEC 8.1 ± 0.1 www.DataSheet4U.com 48 TA3 ...

Page 3

Electrical Characteristics Vcc = 3.0 - 3.6V -10 - +70 ˚C SYMBOL PARAMETER CMOS/TTL DC SPECIFICATIONS V IH High Level Input Voltage V IL Low Level Input Voltage V OH High Level output Voltage V OL Low Level ...

Page 4

Supply Current Vcc = 3.0 - 3.6V -10 - +70 ˚C SYMBOL PARAMETER I TCCG Transmitter Supply Current I TCCW Transmitter Supply Current Transmitter Power Down I TCCS Supply Current I RCCG Receiver Supply Current I RCCW Receiver ...

Page 5

Switching Characteristics Vcc = 3.0 - 3.6V -10 - +70 ˚C SYMBOL PARAMETER TRANSMITTER t CLK IN Transition Time TCIT t CLK IN Period TCP t CLK IN High Time TCH t CLK IN Low Time TCL t ...

Page 6

... CLK IN 2.0V Tx0-Tx6 0.8V Tx+/- TCLK+ Vdiff=0V t TOP1 t TOP0 t TOP6 t TOP5 t TOP4 t TOP3 t TOP2 Note: 1) CLK IN: for THC63LVDM63A(R/F=GND), denoted as solid line, for THC63LVDM63A(R/F=Vcc), denoted as dashed line 2) Vdiff = (TA+) - (TA-), .... (TCLK+) - (TCLK-) www.DataSheet4U.com t TCP t TCL 2.0V 0.8V 0. 2.0V DATA VALID 0.8V t TCD Tx6 Tx5 Tx4 - 6 - THine 2 ...

Page 7

AC TIMING DIAGRAMS RECEIVER DEVICE Rx+/- Rx6 Rx4 Rx5 RCLK+ 2.0V CLK OUT Rx0-Rx6 Note: 1) Vdiff = (RA+) - (RA-), .... (RCLK+) - (RCLK-) www.DataSheet4U.com t RIP2 t RIP3 t RIP4 t RIP5 t RIP6 t RIP0 t RIP1 ...

Page 8

AC TIMING DIAGRAMS TRANSMITTER DEVICE TRANSITION TIMES TTL Input LVDS Output Vdiff = (TA+)-(TA-) TA+ 5pF TA- LVDS output load RECEIVER DEVICE TRANSITION TIMES TTL Output TTL output load PHASE LOCK LOOP SET TIME TRANSMITTER DEVICE /PDWN VCC CLK IN ...

Page 9

TOPShine Electronics Corp. 5th. FI.,No. 68, Chou-Tze St.,Nei Hu Dist., Taipei 114, Taiwan Tel: 02-8797-3667 www.DataSheet4U.com Fax: 02-8797-3677 THine ...